### **Service Manual**

# **Tektronix**

CTS 710 SONET Test Set & CTS 750 SDH Test Set

070-8853-02

#### Warning

The servicing instructions are for use by qualified personnel only. To avoid personal injury, do not perform any servicing unless you are qualified to do so. Refer to the Safety Summary prior to performing service.

Copyright © Tektronix, Inc. All rights reserved. Licensed software products are owned by Tektronix or its suppliers and are protected by United States copyright laws and international treaty provisions.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013, or subparagraphs (c)(1) and (2) of the Commercial Computer Software – Restricted Rights clause at FAR 52.227-19, as applicable.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specifications and price change privileges reserved.

Printed in the U.S.A.

Tektronix, Inc., P.O. Box 1000, Wilsonville, OR 97070-1000

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

#### WARRANTY

Tektronix warrants that this product will be free from defects in materials and workmanship for a period of three (3) years from the date of shipment. If any such product proves defective during this warranty period, Tektronix, at its option, either will repair the defective product without charge for parts and labor, or will provide a replacement in exchange for the defective product.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period and make suitable arrangements for the performance of service. Customer shall be responsible for packaging and shipping the defective product to the service center designated by Tektronix, with shipping charges prepaid. Tektronix shall pay for the return of the product to Customer if the shipment is to a location within the country in which the Tektronix service center is located. Customer shall be responsible for paying all shipping charges, duties, taxes, and any other charges for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or inadequate maintenance and care. Tektronix shall not be obligated to furnish service under this warranty a) to repair damage resulting from attempts by personnel other than Tektronix representatives to install, repair or service the product; b) to repair damage resulting from improper use or connection to incompatible equipment; or c) to service a product that has been modified or integrated with other products when the effect of such modification or integration increases the time or difficulty of servicing the product.

THIS WARRANTY IS GIVEN BY TEKTRONIX WITH RESPECT TO THIS PRODUCT IN LIEU OF ANY OTHER WARRANTIES, EXPRESSED OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

# **Contents**

|                       | General Safety Summary                                                                                                                         | X                                         |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

|                       | Service Safety Summary                                                                                                                         | XV                                        |

|                       | Preface Conventions Related Manuals                                                                                                            | <b>xvi</b> i<br>xvii<br>xix               |

|                       | Introduction                                                                                                                                   | xxi<br>xxi<br>xxi                         |

| Specifications        |                                                                                                                                                |                                           |

|                       | Product Description Guide to the Specifications Performance Conditions CTS 710 Specification Tables CTS 750 Specification Tables               | 1–1<br>1–2<br>1–2<br>1–3<br>1–17          |

| Operating Information | n                                                                                                                                              |                                           |

|                       | Installation  Supplying Operating Power  Operating Environment  Applying and Interrupting Power  Installed Options                             | <b>2–1</b> 2–1 2–3 2–4 2–4                |

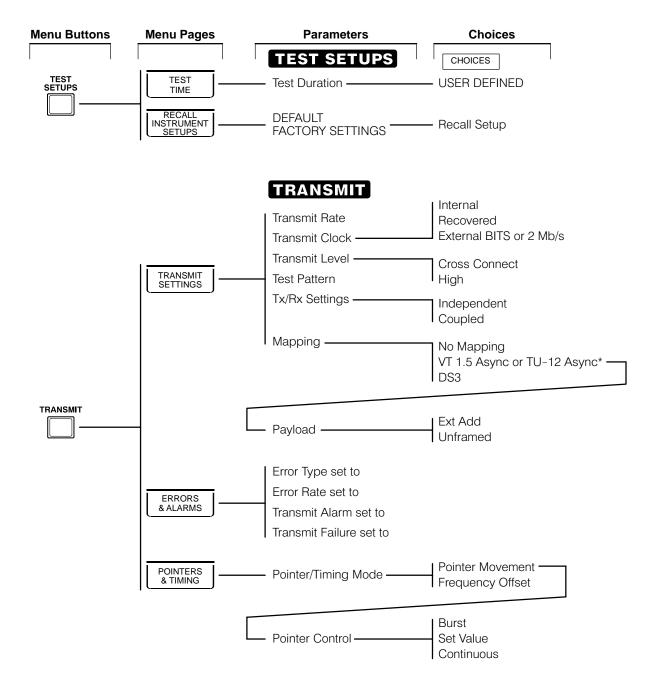

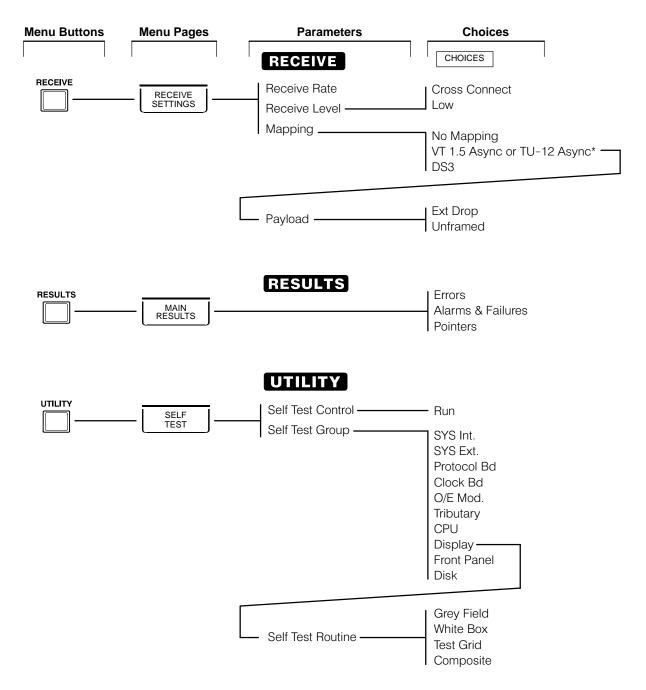

|                       | Operating Information  Front-Panel Controls and Indicators Rear-Panel Controls and Connections Front-Panel Status Lights Using the Menu System | 2-5<br>2-5<br>2-6<br>2-7<br>2-8           |

| Theory of Operation   |                                                                                                                                                |                                           |

|                       | Module Descriptions                                                                                                                            | 3–1                                       |

| Performance Verifica  | tion                                                                                                                                           |                                           |

|                       | General Information and Conventions  Equipment Required  Test Record  Self Test  Functional Tests  Physical Layer Tests                        | 4-2<br>4-3<br>4-8<br>4-14<br>4-15<br>4-20 |

| Adjustment Procedur   | res                                                                                                                                            |                                           |

|                       | Equipment Required                                                                                                                             | 5–1<br>5–2                                |

### Maintenance

| Preparation                                                           | 0-1   |

|-----------------------------------------------------------------------|-------|

| Inspection and Cleaning                                               | 6–3   |

| General Care                                                          | 6–3   |

| Inspection and Cleaning Procedures                                    | 6–3   |

| Removal and Replacement                                               | 6–9   |

| Preparation                                                           | 6–9   |

| Access Procedure                                                      | 6–11  |

| Procedures for Module Removal and Installation                        | 6–22  |

| Optical Port Connector                                                | 6–22  |

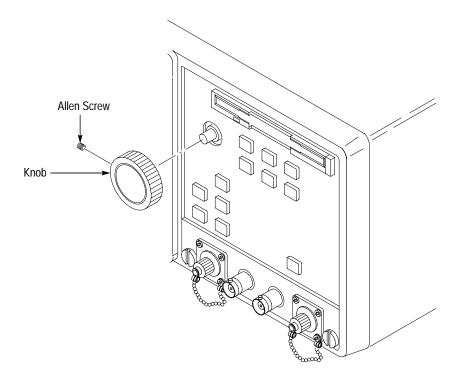

| Front-Panel Knob                                                      | 6–24  |

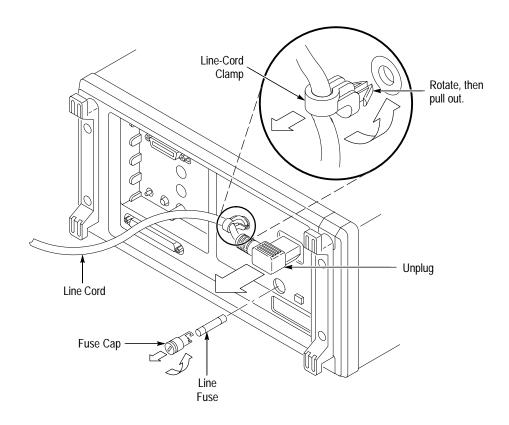

| Line Fuse and Line Cord                                               | 6–26  |

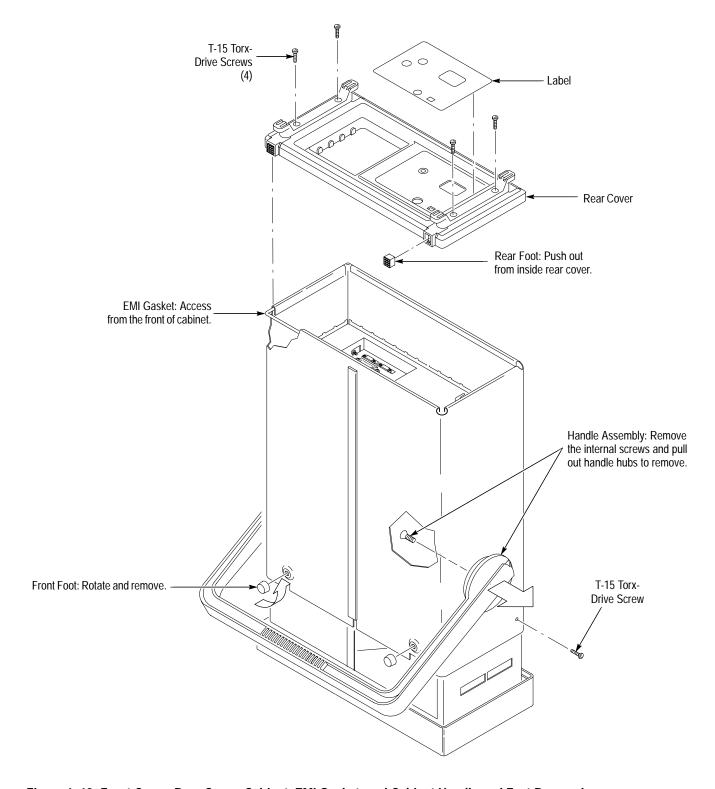

| Front Cover, Rear Cover, Cabinet, Rear EMI Gasket, and Cabinet Handle |       |

| and Feet                                                              | 6–27  |

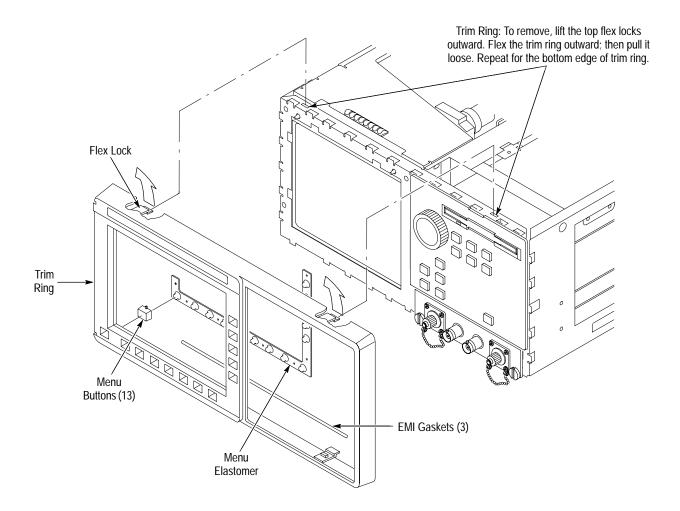

| Trim Ring, Menu Elastomer, Menu Buttons, and Front EMI Gaskets        | 6-30  |

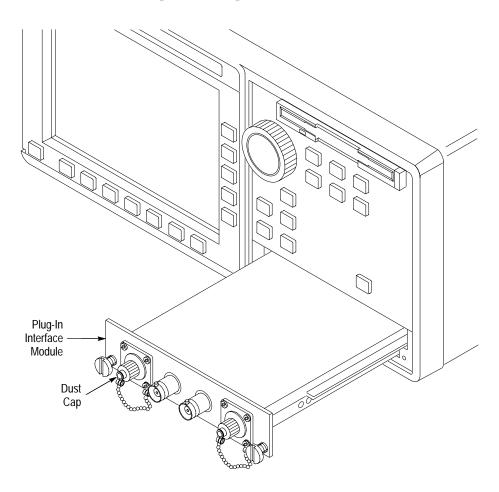

| Plug-In Interface Module                                              | 6–33  |

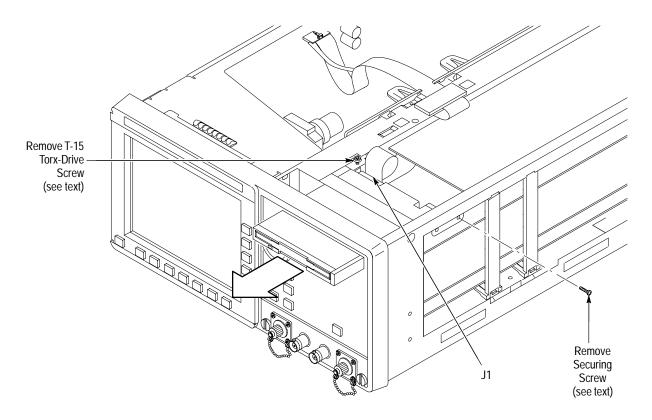

| Disk Drive                                                            | 6-34  |

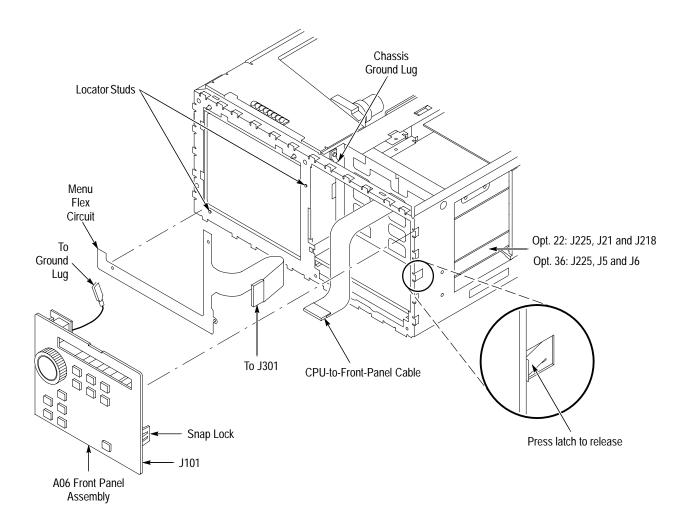

| A06 Front Panel Assembly and Menu Flex Circuit                        | 6-35  |

| A10 High Speed Protocol Assembly                                      | 6-39  |

| A09 Main Protocol Assembly                                            | 6-41  |

| A26 Monitor Assembly                                                  | 6-42  |

| Com Bus, Board Supports, and PCAT Bus                                 | 6-45  |

| EMI Shield                                                            | 6-46  |

| A03 CPU Assembly                                                      | 6–47  |

| A01 Display Assembly                                                  | 6-49  |

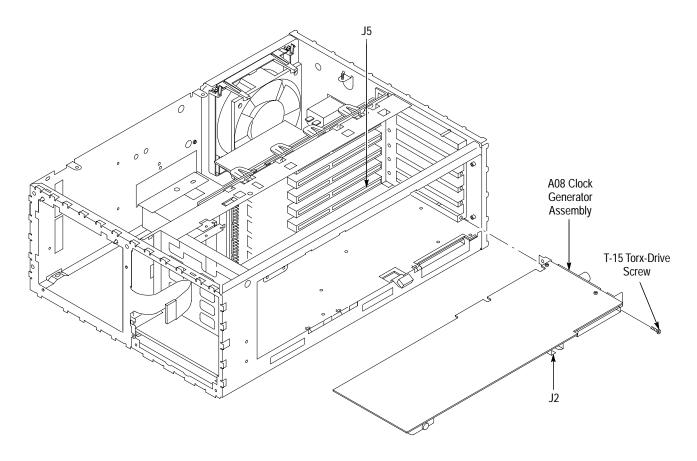

| A08 Clock Generator Assembly                                          | 6-50  |

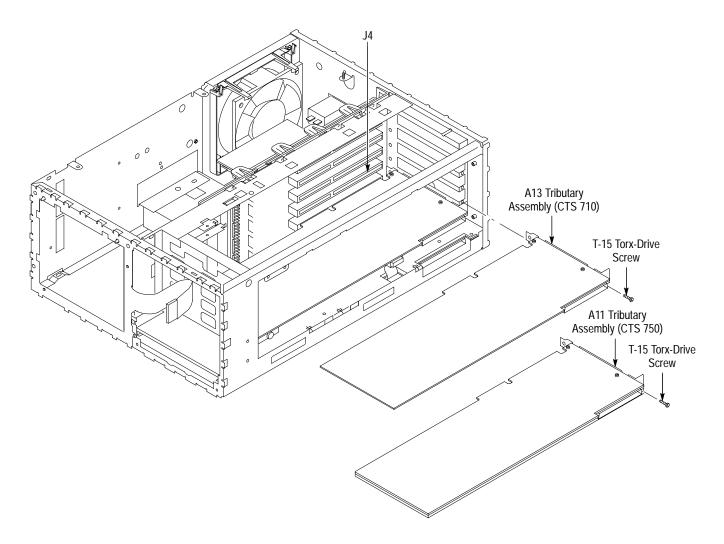

| Tributary Assembly                                                    | 6-51  |

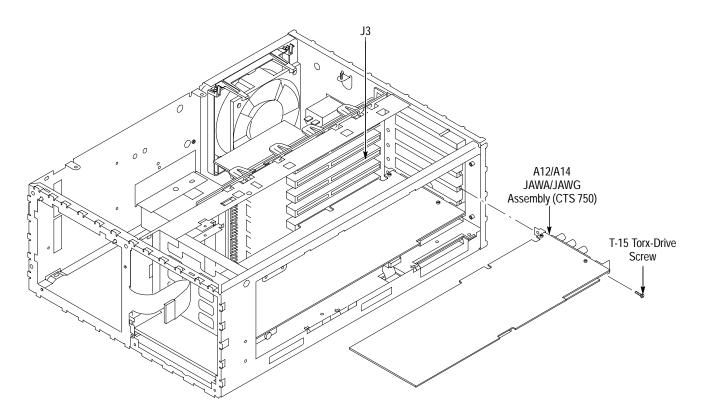

| JAWA/JAWG Assembly                                                    | 6-53  |

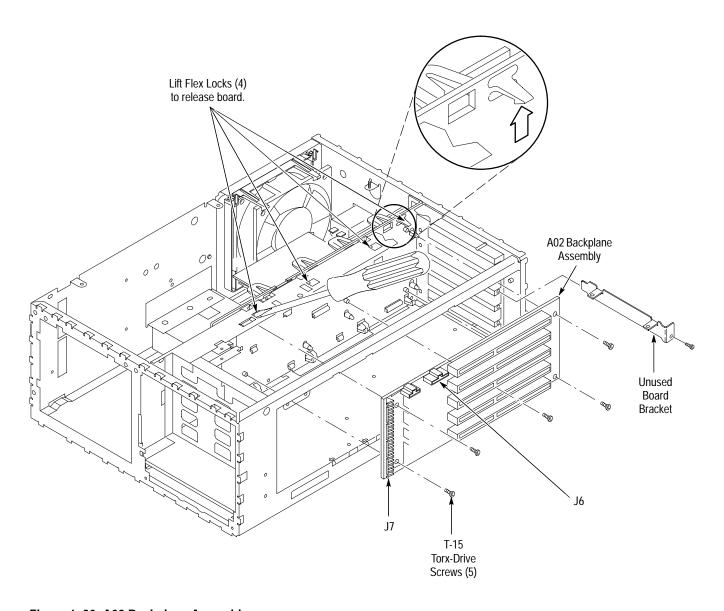

| A02 Backplane Assembly                                                | 6-55  |

| Back-Up Battery                                                       | 6-56  |

| Fan and Fan Mount                                                     | 6-58  |

| A25 Low Voltage Power Supply and its Mount                            | 6-60  |

| A07 Auxiliary Power Supply                                            | 6-62  |

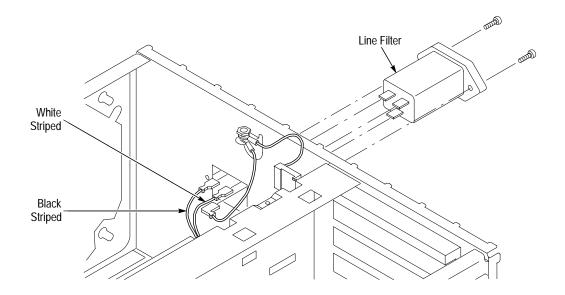

| Line Filter                                                           | 6-63  |

| Main Chassis                                                          | 6-64  |

| Disassembly for Cleaning                                              | 6-65  |

| Troubleshooting                                                       | 6-69  |

| Diagnostics                                                           | 6–69  |

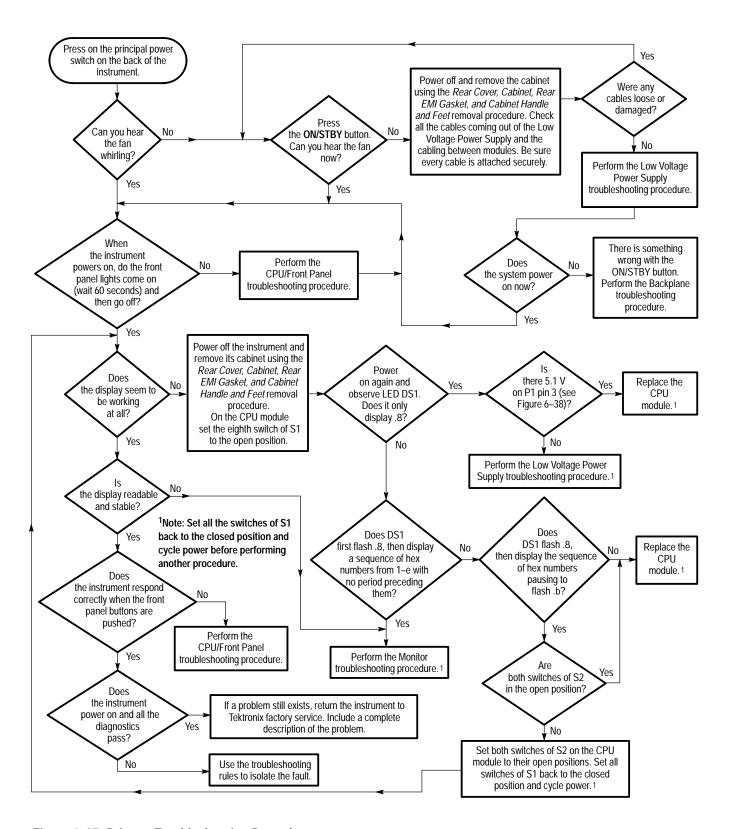

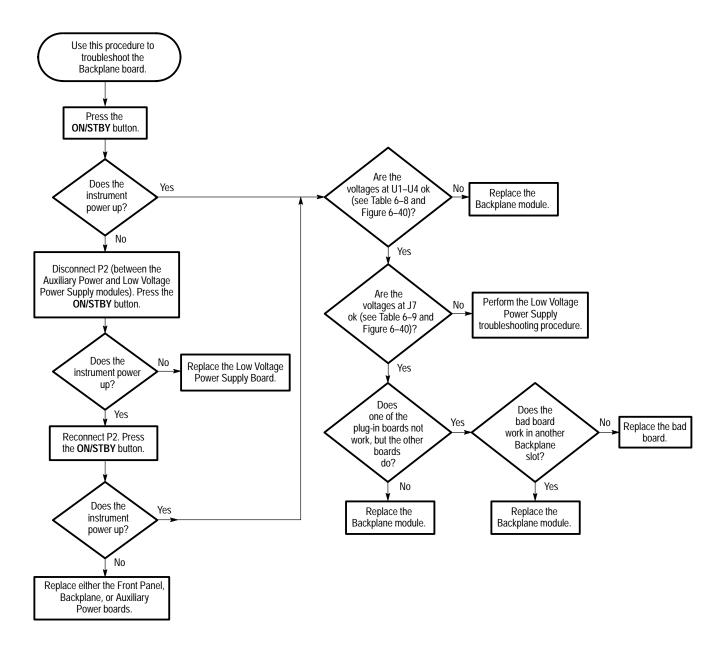

| Troubleshooting Trees                                                 | 6–70  |

| Shared Routines                                                       | 6–86  |

| Tributary Shared Routines                                             | 6–89  |

| Diagnostic Test Descriptions                                          | 6–99  |

| Front Panel General Notes                                             | 6–126 |

| Front Panel Error Messages                                            | 6–126 |

| Tributary General Notes                                               | 6–133 |

| Jitter/Wander General Notes                                           | 6–139 |

| Troubleshooting Sequence                                              | 6–145 |

| After-Repair Adjustments                                              | 6–157 |

| -                                                                     |       |

| Renackaging Instructions                                              | 6-159 |

## **Options**

| Floatrical Douts List | Options               | 7–1  |

|-----------------------|-----------------------|------|

| Electrical Parts List | Electrical Parts List | 8–1  |

| Diagrams              | Diagrams              | 9–1  |

| Mechanical Parts List | Mechanical Parts List | 10–1 |

# **List of Figures**

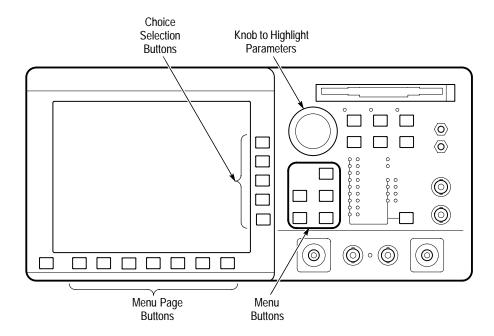

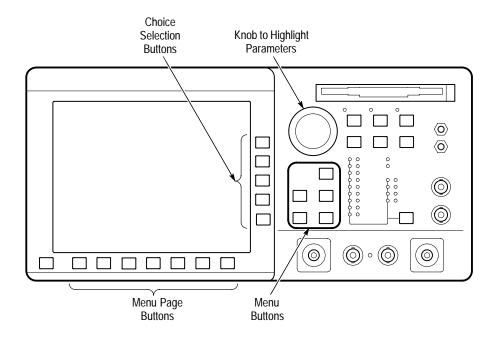

| Figure 2–1: Controls Located Around the Display               | 2–5  |

|---------------------------------------------------------------|------|

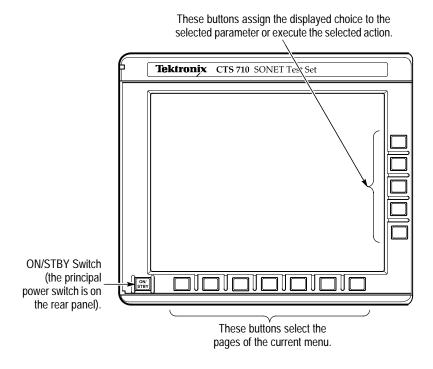

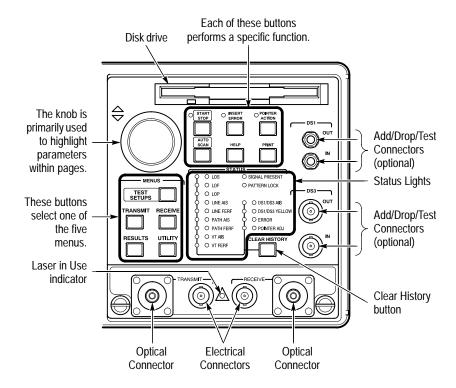

| Figure 2–2: Front-Panel Controls and Indicators               | 2–6  |

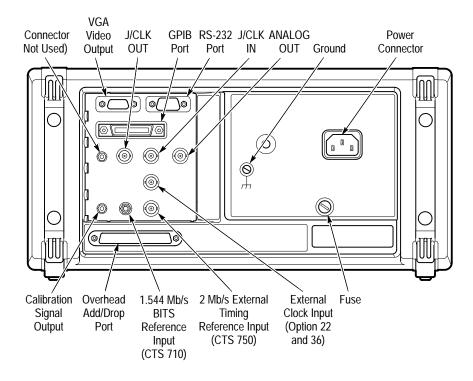

| Figure 2–3: Rear-Panel Controls and Connections               | 2–7  |

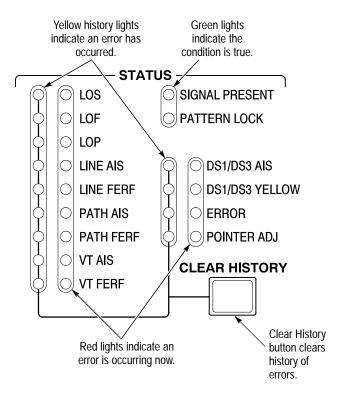

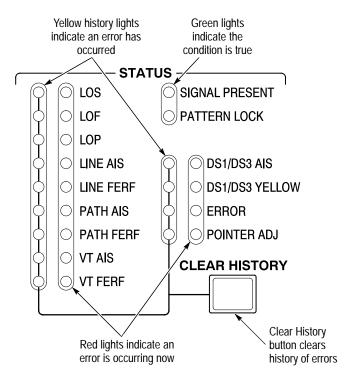

| Figure 2–4: Status Lights                                     | 2–8  |

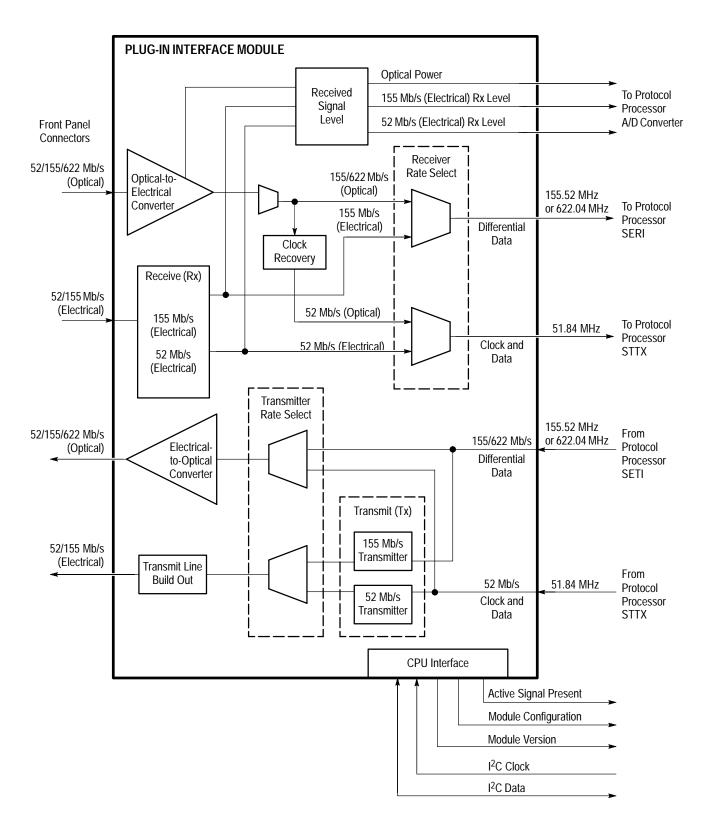

| Figure 3–1: Plug-In Interface Module Functional Block Diagram | 3–3  |

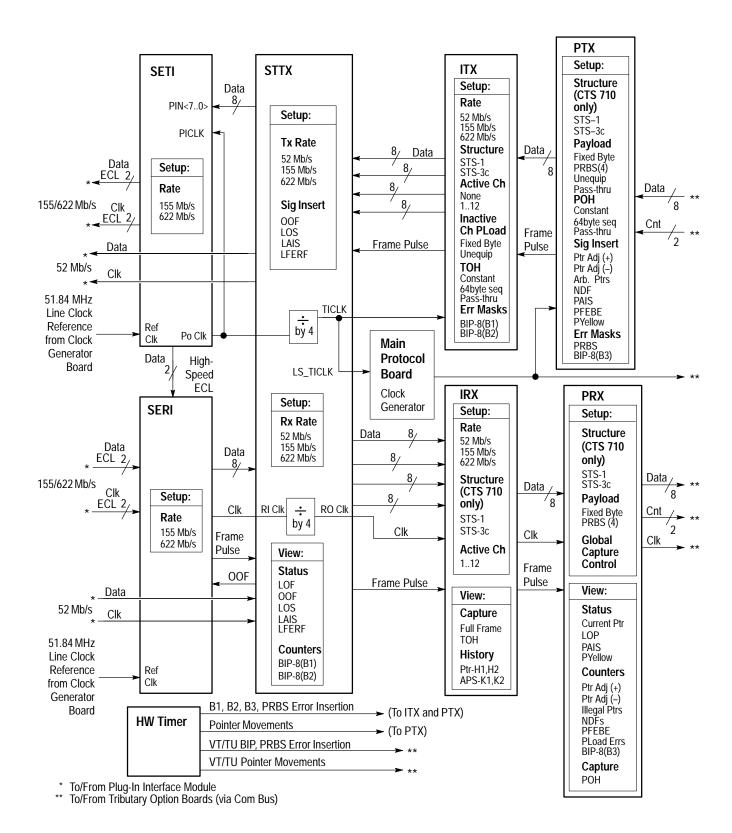

| Figure 3–2: Protocol Processor Functional Block Diagram       | 3–9  |

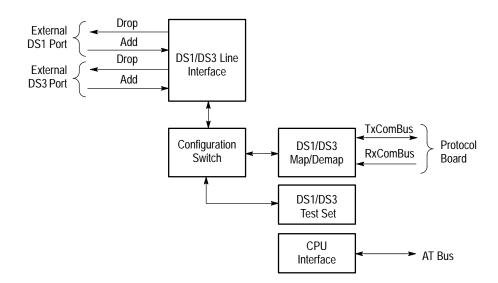

| Figure 3–3: DS1/DS3 Add/Drop/Test Block Diagram               | 3–11 |

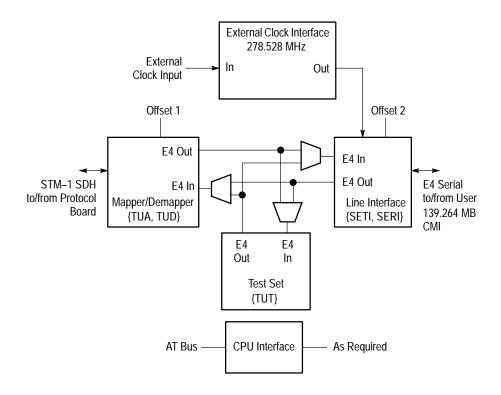

| Figure 3–4: E4 Block Diagram                                  |      |

| (E1/E3 Support Functions Not Included)                        | 3–13 |

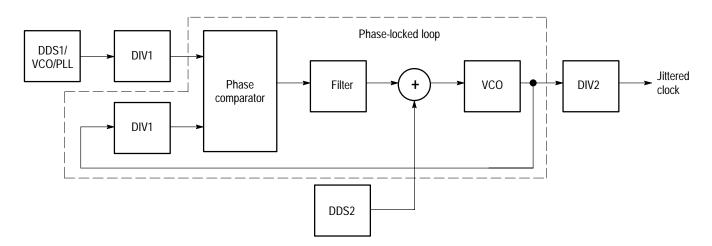

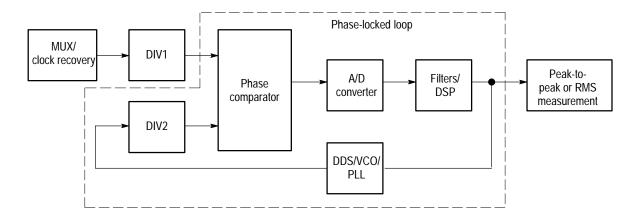

| Figure 3-5: JAWG Block Diagram                                | 3–14 |

| Figure 3–6: JAWA Block Diagram                                | 3–16 |

| Figure 4–1: Location of Front-Panel Controls                  | 4–3  |

| Figure 4–2: Typical Front-Panel Status Lights                 | 4–15 |

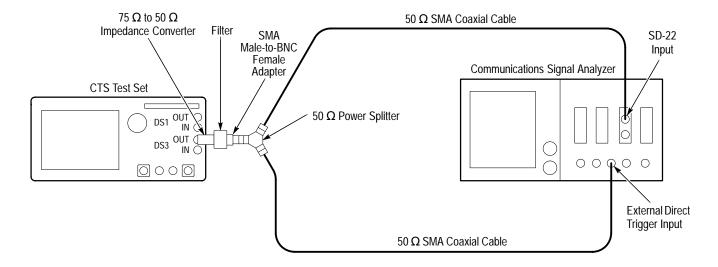

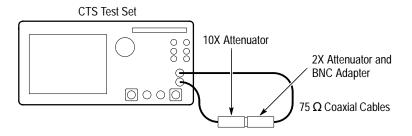

| Figure 4–3: Transmit Electrical Output Amplitude Hookup       | 4–21 |

| Figure 4–4: Transmit Level Hookup                             | 4–23 |

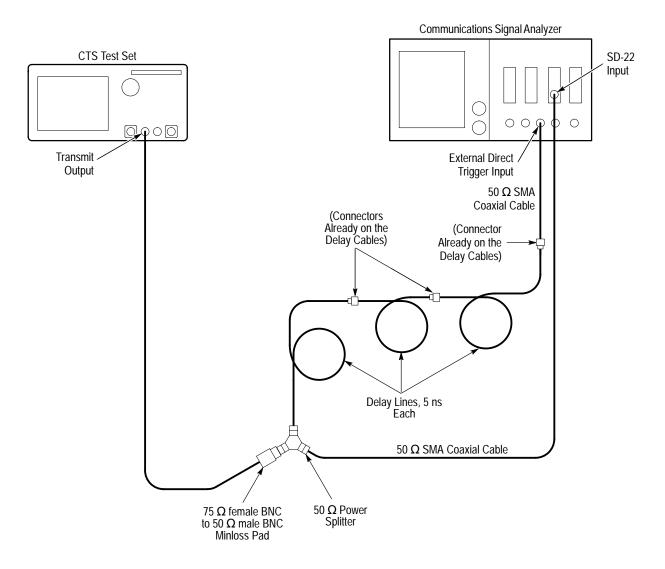

| Figure 4–5: Transmit Electrical Output Pulse Shape Hookup     | 4–27 |

| Figure 4–6: Transmit Optical Output Pulse Shape Hookup        | 4–34 |

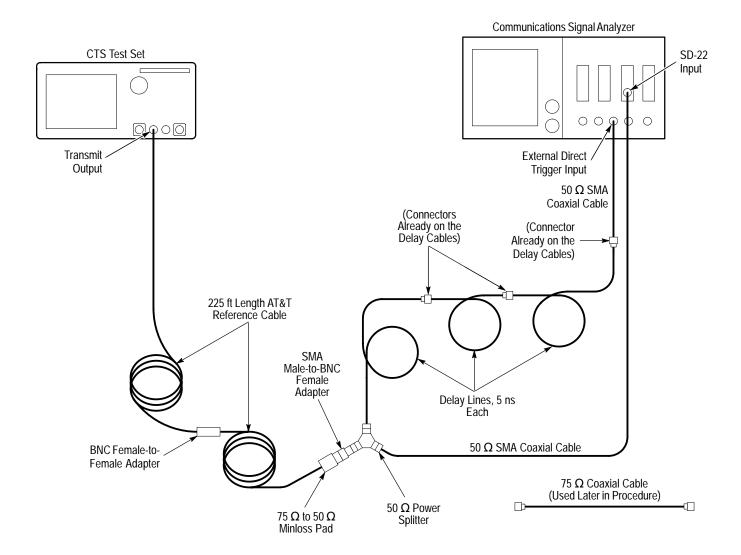

| Figure 4–7: Receive Electrical Input Sensitivity Hookup       | 4–38 |

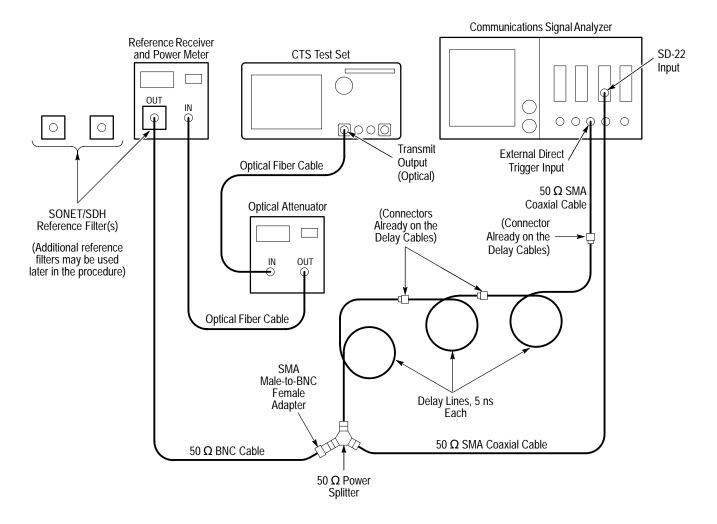

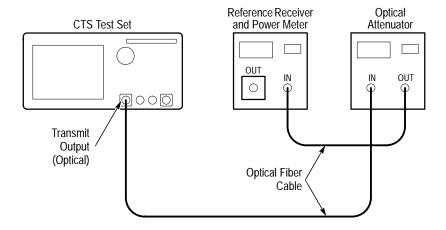

| Figure 4–8: Receive Optical Input Sensitivity Hookup          | 4-43 |

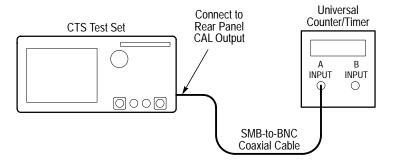

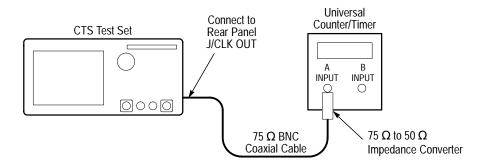

| Figure 4–9: Internal Clock Accuracy Hookup                    | 4–46 |

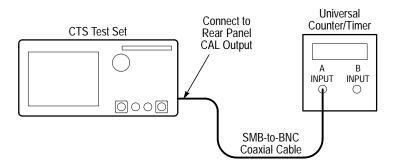

| Figure 4–10: Transmit Line Frequency Offset Hookup            | 4-48 |

| Figure 4–11: Transmit Line Frequency Offset Hookup            | 4–50 |

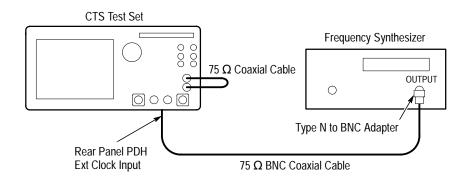

| Figure 4–12: BITS Reference Frequency-Lock Hookup             | 4–52 |

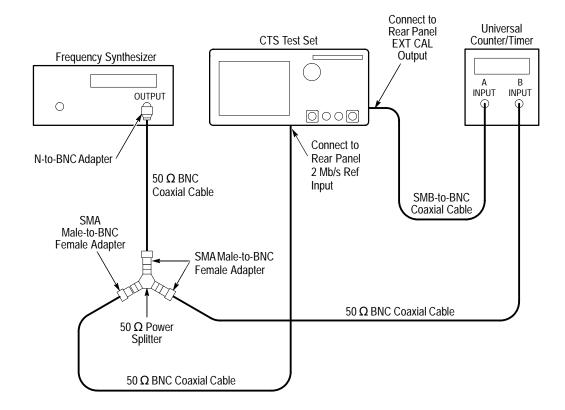

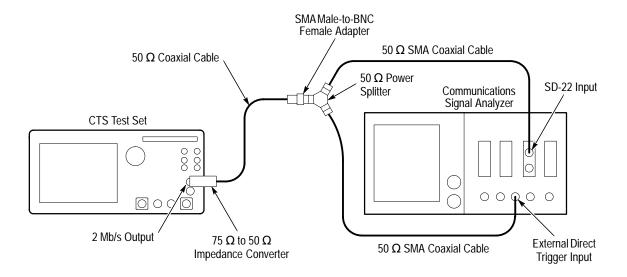

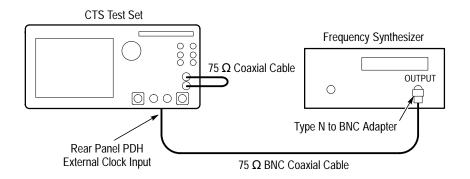

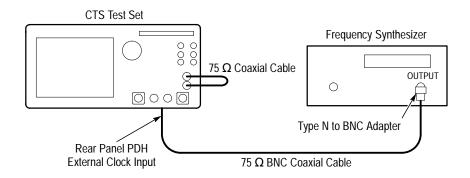

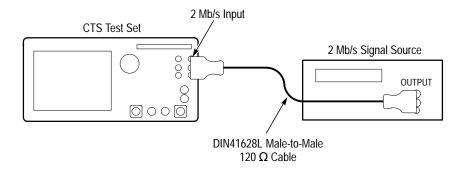

| Figure 4–13: 2 Mb/s Reference Frequency-Lock Hookup           | 4–54 |

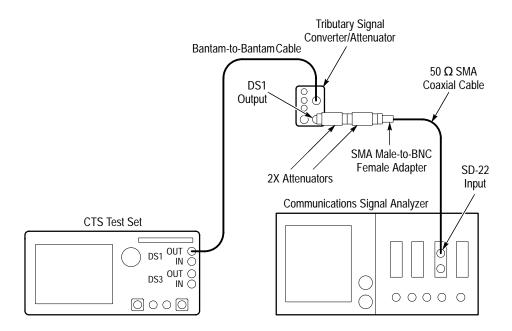

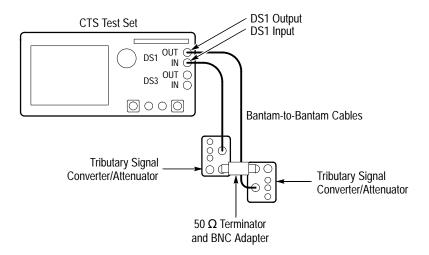

| Figure 4–14: DS1 Signal Level Hookup                          | 4–57 |

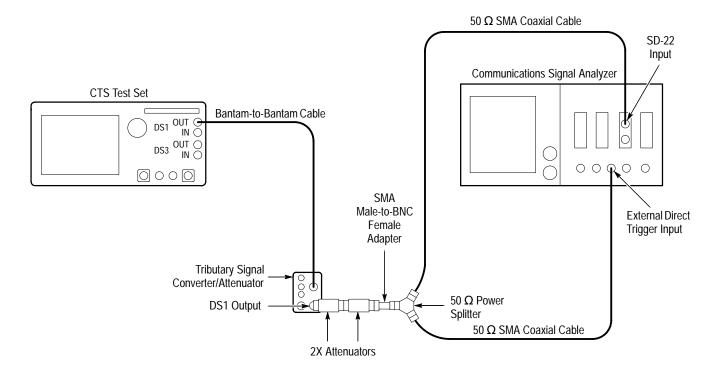

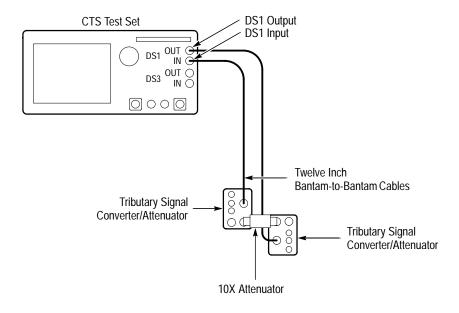

| Figure 4–15: DS1 Pulse Shape Hookup                           | 4–59 |

| Figure 4–16: DS1 Data Formats Hookup                          | 4–61 |

| Figure 4–17: DS1 Monitor Receive Level Hookup                 | 4–63 |

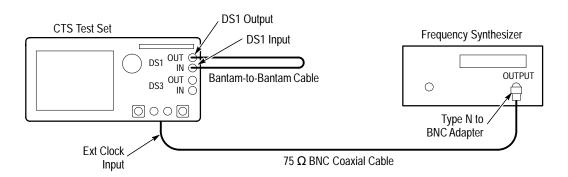

| Figure 4–18: DS1 External Clock Hookup                        | 4–65 |

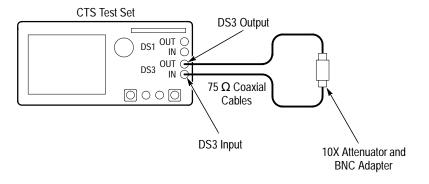

| Figure 4–19: DS3 Signal Level Hookup                          | 4–67 |

| Figure 4–20: DS3 Pulse Shape Hookup                           | 4–69 |

| Figure 4–21: DS3 Monitor Receive Level Hookup                 | 4–72 |

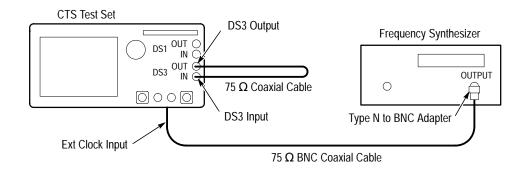

| Figure 4–22: DS3 External Clock Hookup                        | 4–74 |

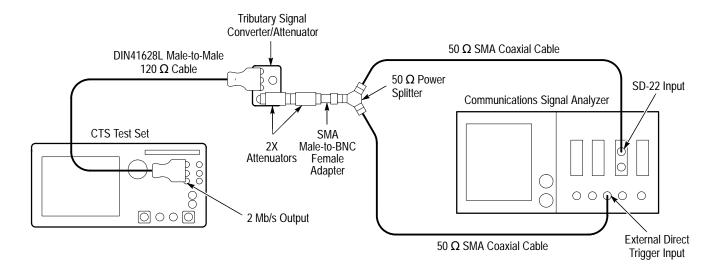

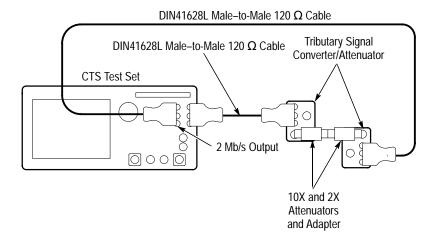

| Figure 4–23: 2 Mb/s Pulse Mask Hookup                         | 4_77 |

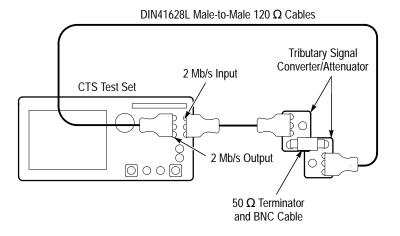

| Figure 4–24: 2 Mb/s Monitor Receive Level Hookup                | 4–80  |

|-----------------------------------------------------------------|-------|

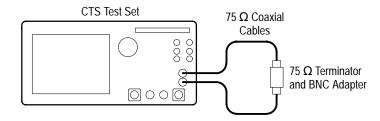

| Figure 4–25: 2 Mb/s Bridged Hookup                              | 4–82  |

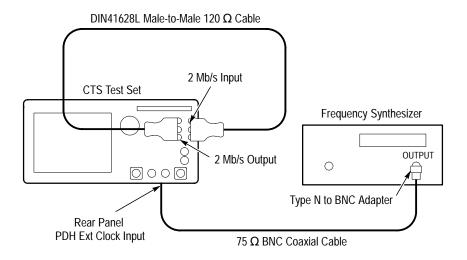

| Figure 4–26: 2 Mb/s External Clock Hookup                       | 4–84  |

| Figure 4–27: 2 Mb/s Pulse Mask Hookup                           | 4–86  |

| Figure 4–28: 34 Mb/s Pulse Mask Hookup                          | 4–90  |

| Figure 4–29: 140 Mb/s Transmit Pulse Mask Hookup                | 4–93  |

| Figure 4–30: 2 Mb/s Bridged Hookup                              | 4–96  |

| Figure 4–31: 2 Mb/s Monitor Receive Level Hookup                | 4–98  |

| Figure 4–32: 34 Mb/s Monitor Receive Level Hookup               | 4_99  |

| Figure 4–33: 140 Mb/s Monitor Receive Level Hookup              | 4–100 |

| Figure 4–34: 2 Mb/s External Clock Hookup                       | 4–102 |

| Figure 4–35: 34 Mb/s External Clock Hookup                      | 4–104 |

| Figure 4–36: 140 Mb/s External Clock Hookup                     | 4–106 |

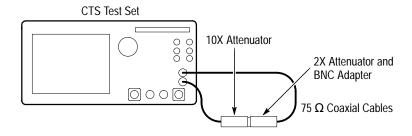

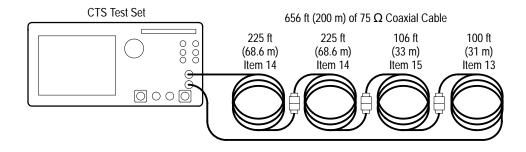

| Figure 4–37: 2 Mb/s Cable Equalization Hookup                   | 4–108 |

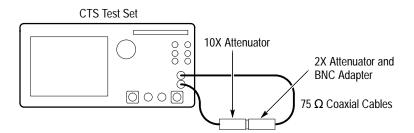

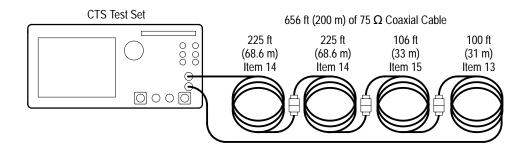

| Figure 4–38: 34 Mb/s Cable Equalization Hookup                  | 4–109 |

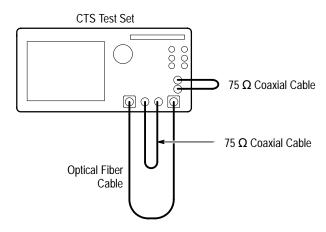

| Figure 4–39: 140 Mb/s Cable Equalization Hookup                 | 4–110 |

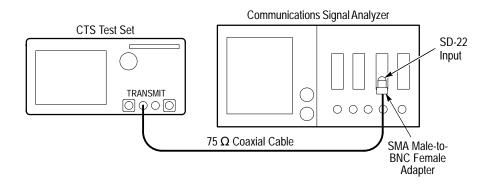

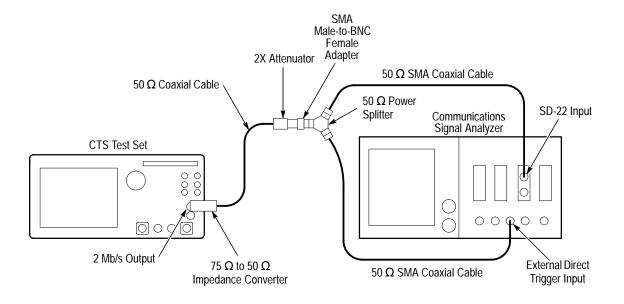

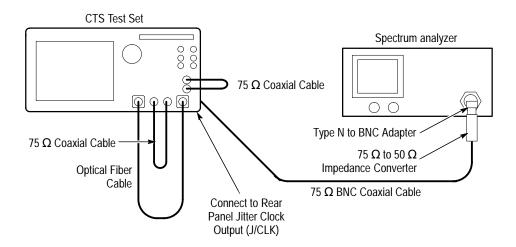

| Figure 4–40: Low-Frequency Jitter Test Hookup                   | 4–111 |

| Figure 4–41: High Amplitude Jitter Test Hookup                  | 4–115 |

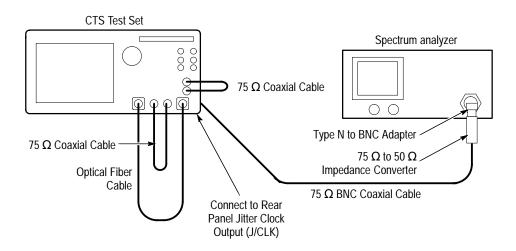

| Figure 4–42: High Amplitude Jitter Test Hookup                  | 4–123 |

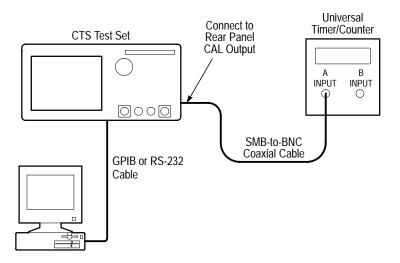

| Figure 5–1: Internal Clock Frequency Adjustment Connections     | 5–4   |

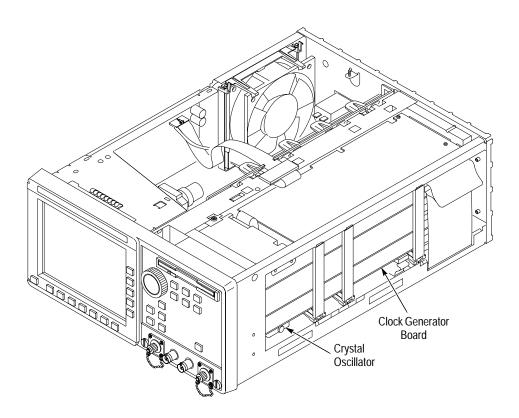

| Figure 5–2: Location of Crystal Oscillator                      | 5–6   |

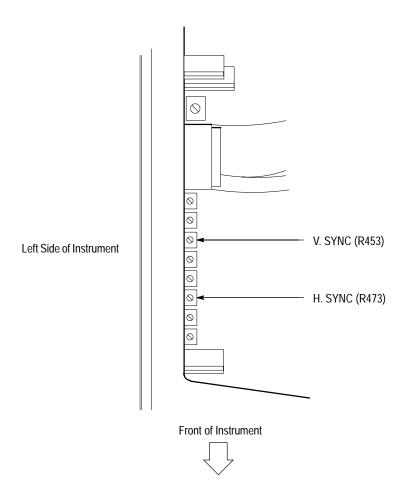

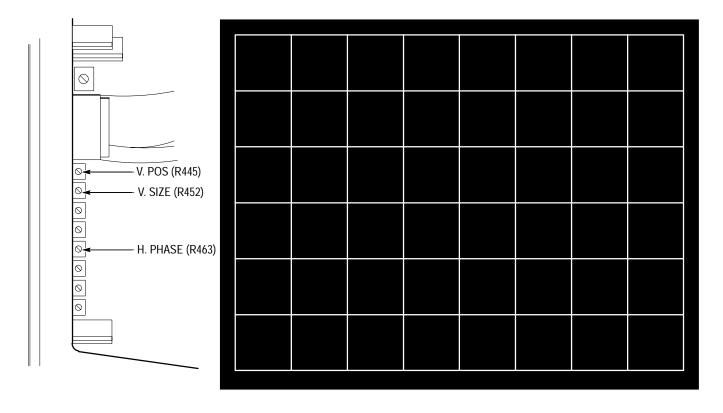

| Figure 5–3: Monitor Adjustment Locations                        | 5–8   |

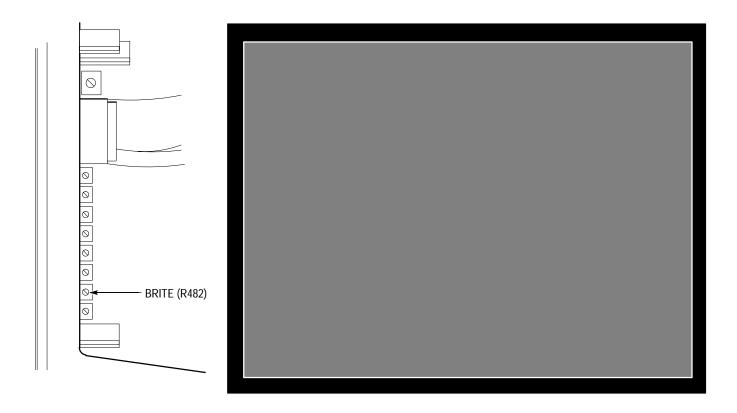

| Figure 5–4: Brightness Adjustment and Gray Field Pattern        | 5–9   |

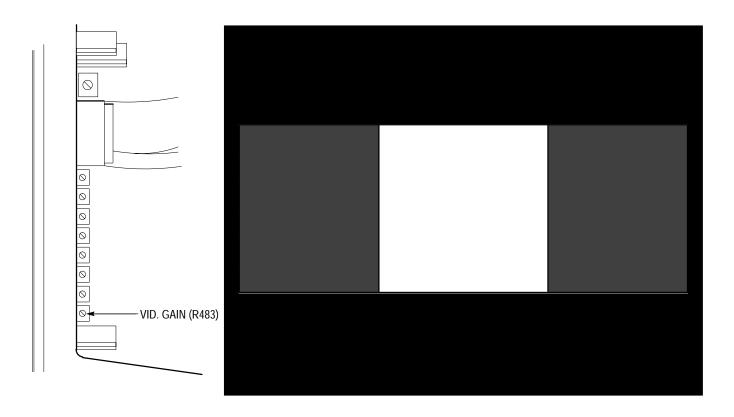

| Figure 5–5: Video Gain Adjustment and White Box Pattern         | 5–10  |

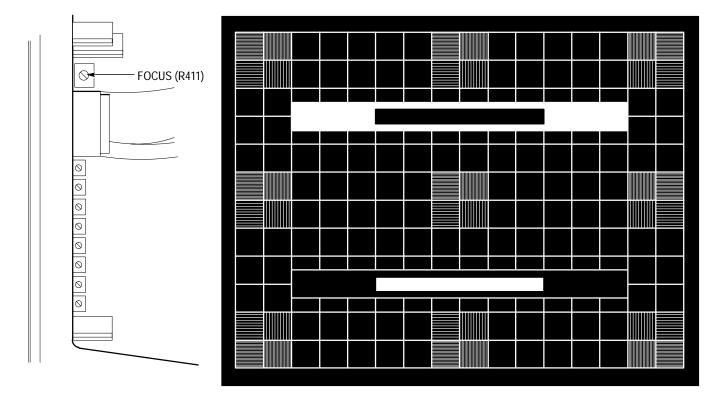

| Figure 5–6: Focus Adjustment and Composite Test Pattern         | 5–11  |

| Figure 5–7: Position and Size Adjustments and Test Grid Pattern | 5–12  |

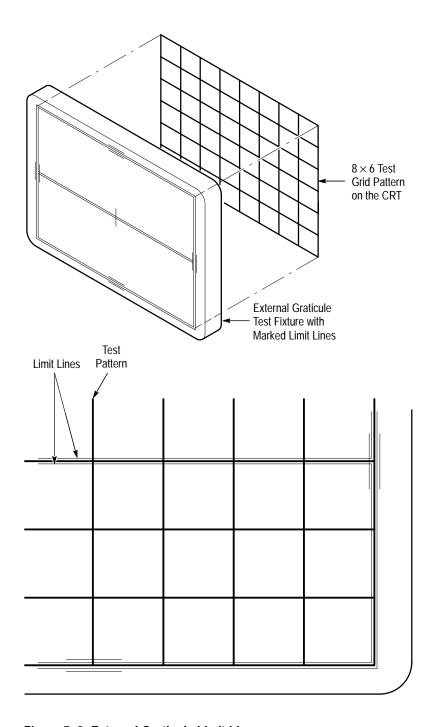

| Figure 5–8: External Graticule Limit Lines                      | 5–13  |

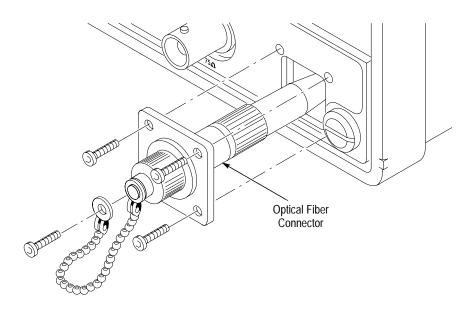

| Figure 6–1: Removing the Optical Bulkhead Connector             | 6–5   |

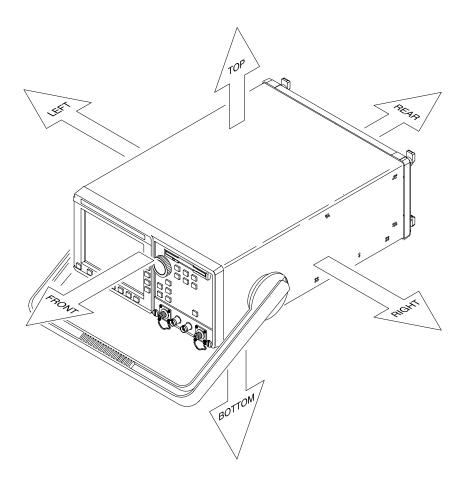

| Figure 6–2: CTS 700-Series Test Set Orientation                 | 6–10  |

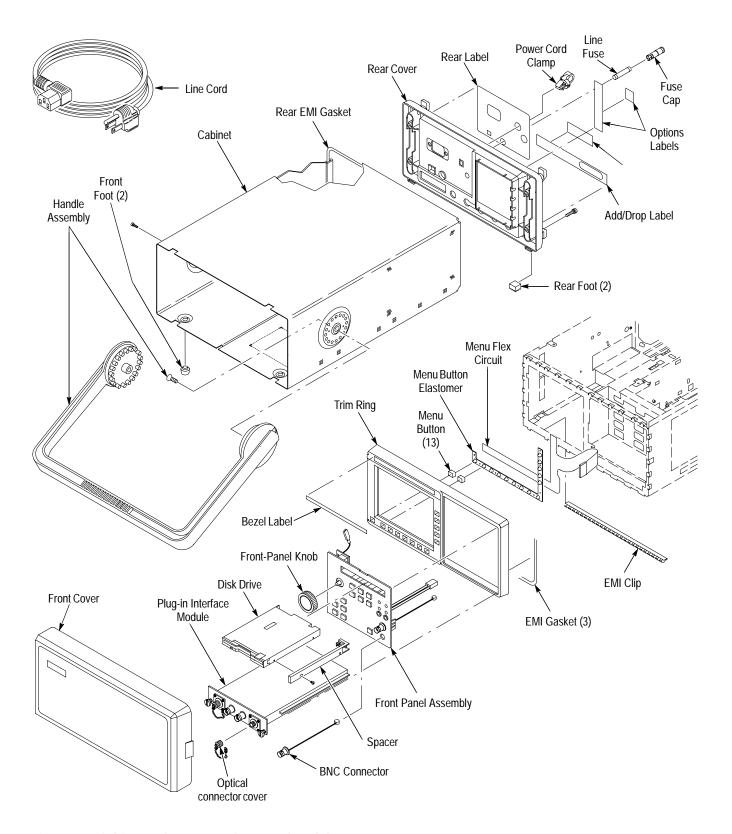

| Figure 6–3: Cabinet and Front-Panel Mounted Modules             | 6–14  |

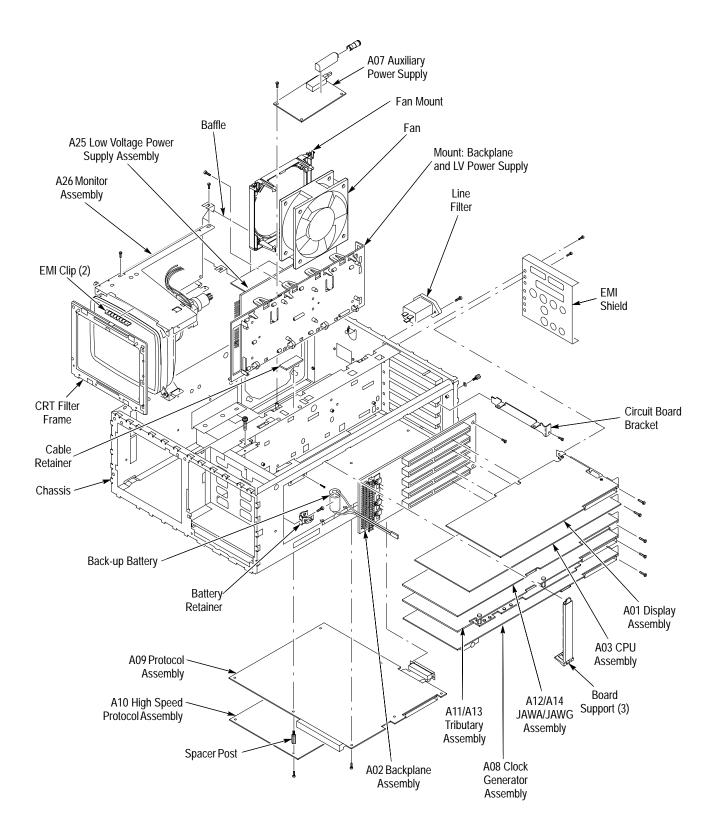

| Figure 6–4: Internal Modules                                    | 6–17  |

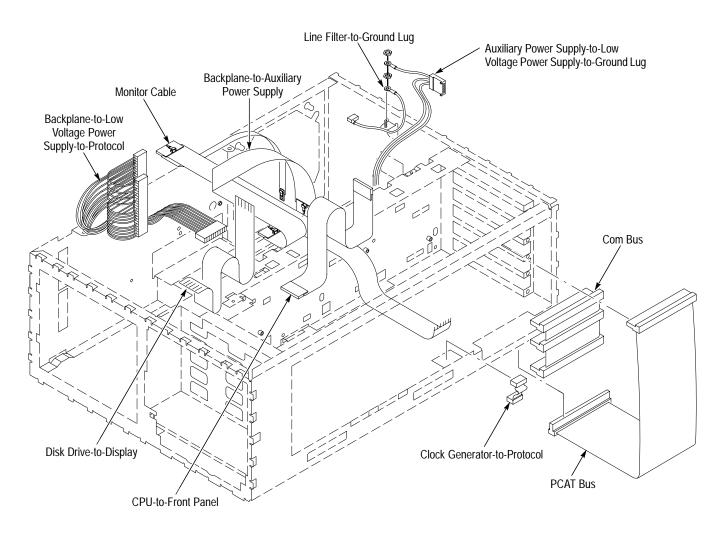

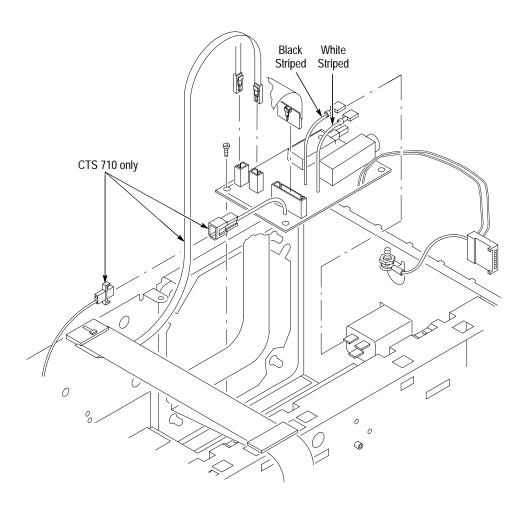

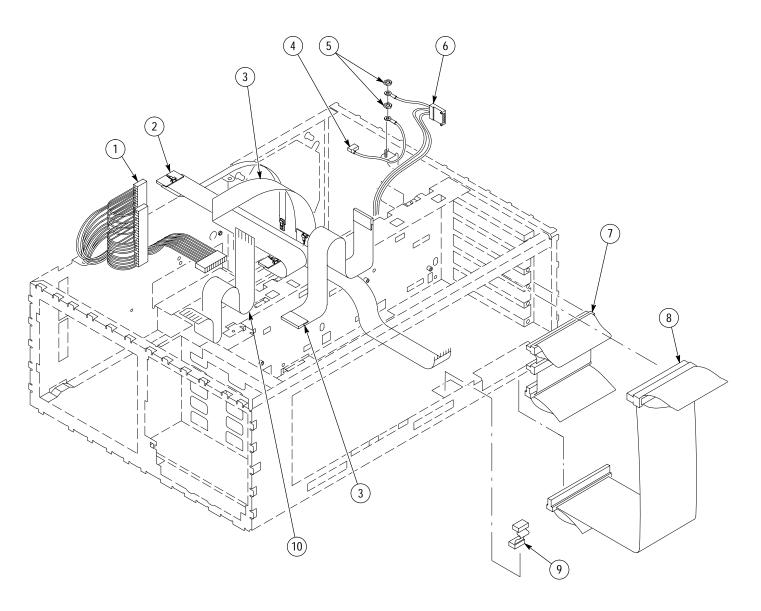

| Figure 6–5: CTS 710 Cables and Cable Routing                    | 6-20  |

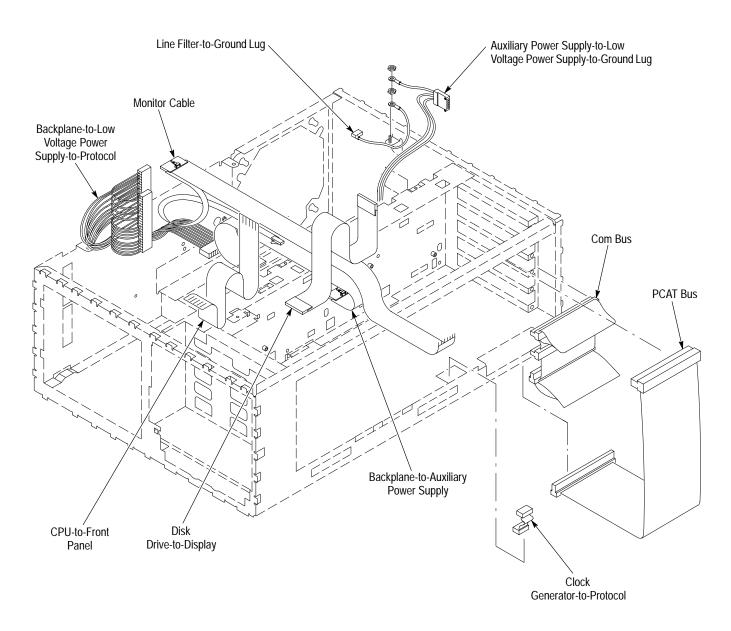

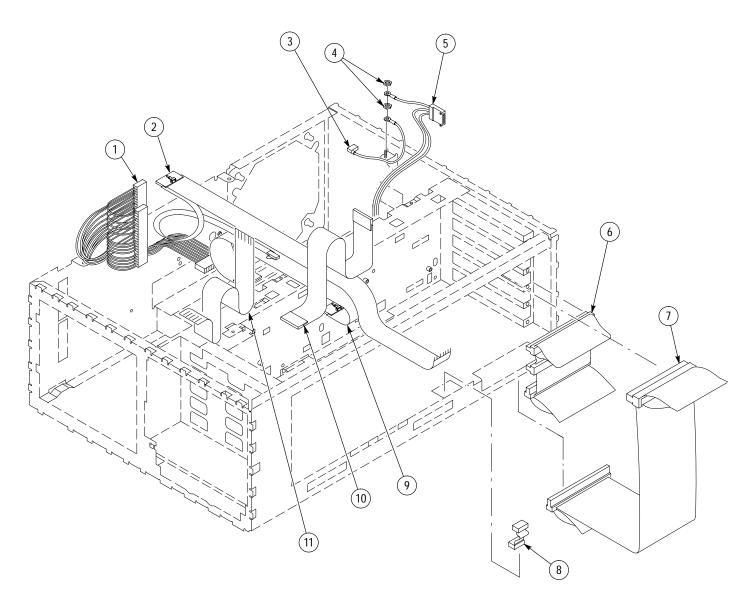

| Figure 6–6: CTS 750 Cables and Cable Routing                    | 6–21  |

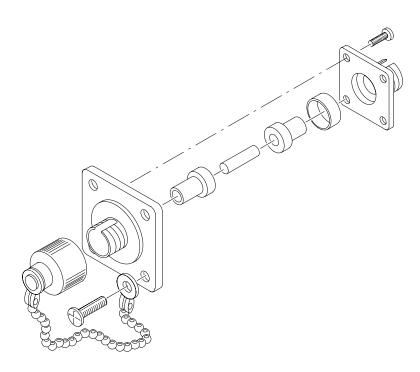

| Figure 6–7: FC Optical Bulkhead Assembly                        | 6–22  |

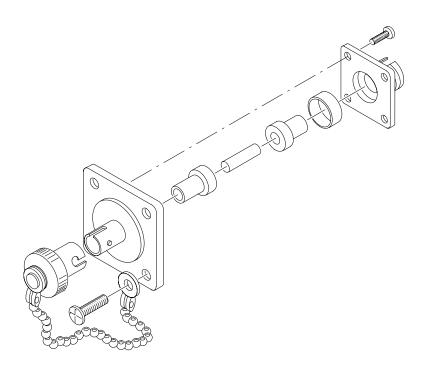

| Figure 6–8: ST Optical Bulkhead Assembly                        | 6–23  |

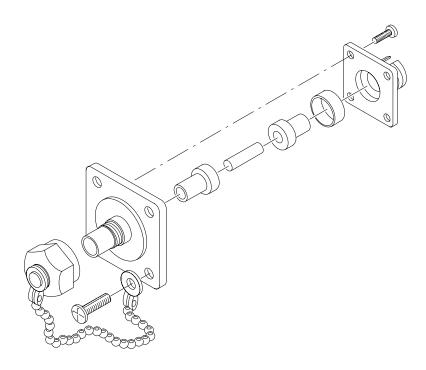

| Figure 6–9: DIN 47256 Optical Bulkhead Assembly                 | 6–23  |

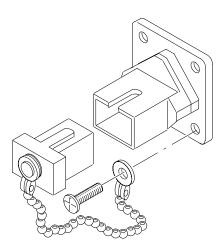

| Figure 6_10: SC Ontical Rulkhead Assembly                       | 6_24  |

| Figure 6–11: Knob Removal                                      | 6–25 |

|----------------------------------------------------------------|------|

| Figure 6–12: Line Fuse and Line Cord Removal                   | 6–26 |

| Figure 6–13: Front Cover, Rear Cover, Cabinet, EMI Gasket, and |      |

| Cabinet Handle and Feet Removal                                | 6–28 |

| Figure 6–14: Trim Ring, Menu Elastomer, and Menu               |      |

| Buttons Removal                                                | 6–31 |

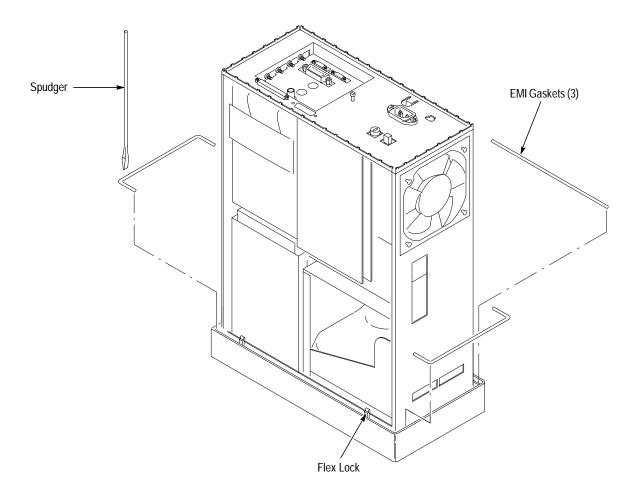

| Figure 6–15: EMI Gasket Installation                           | 6–32 |

| Figure 6–16: Cabinet and Front-Panel Mounted Modules           | 6–33 |

| Figure 6–17: Disk Drive Removal                                | 6–34 |

| Figure 6–18: A06 Front Panel Assembly and Menu Flex            |      |

| Circuit Removal                                                | 6–36 |

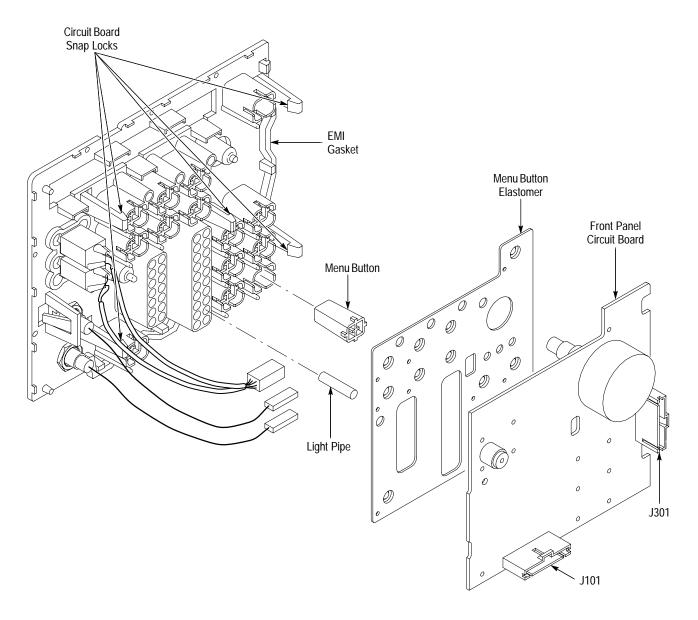

| Figure 6–19: Disassembly of the Front Panel Assembly           | 6–37 |

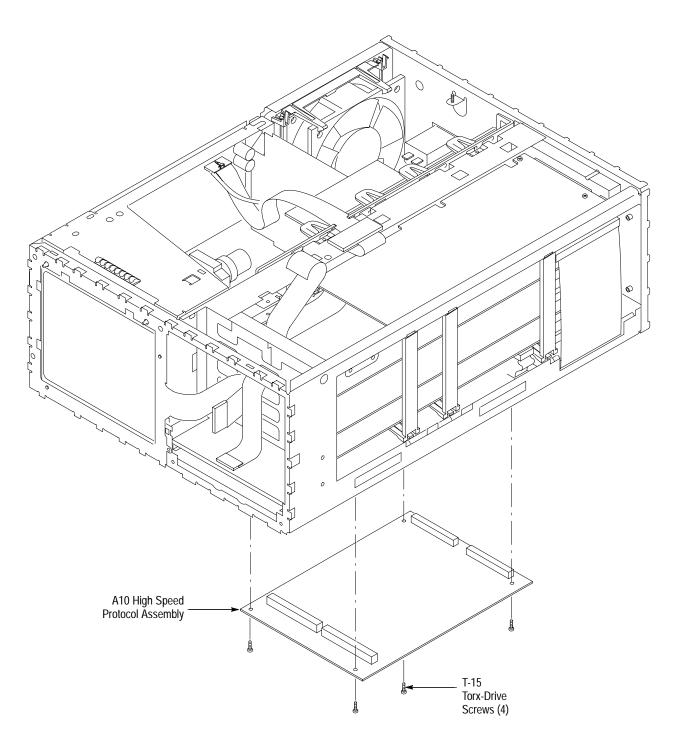

| Figure 6–20: A10 High Speed Protocol Assembly Removal          | 6–40 |

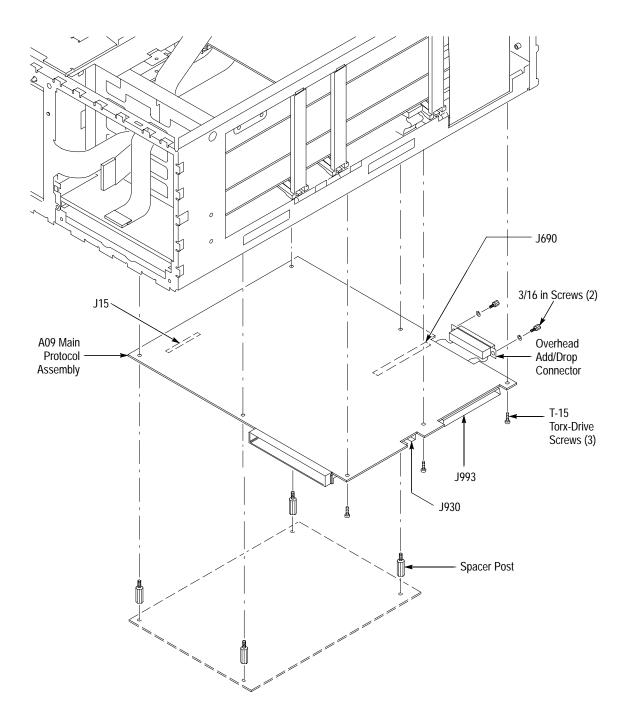

| Figure 6–21: A09 Main Protocol Assembly Removal                | 6–42 |

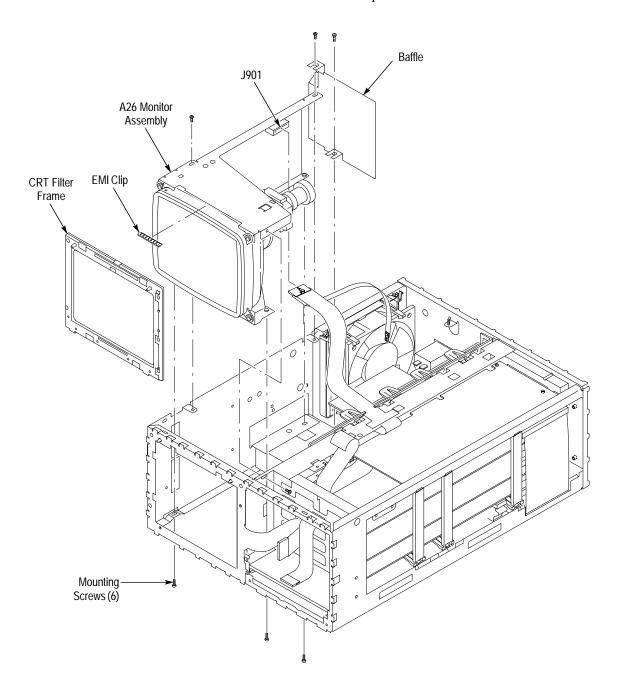

| Figure 6–22: A26 Monitor Assembly Removal                      | 6–44 |

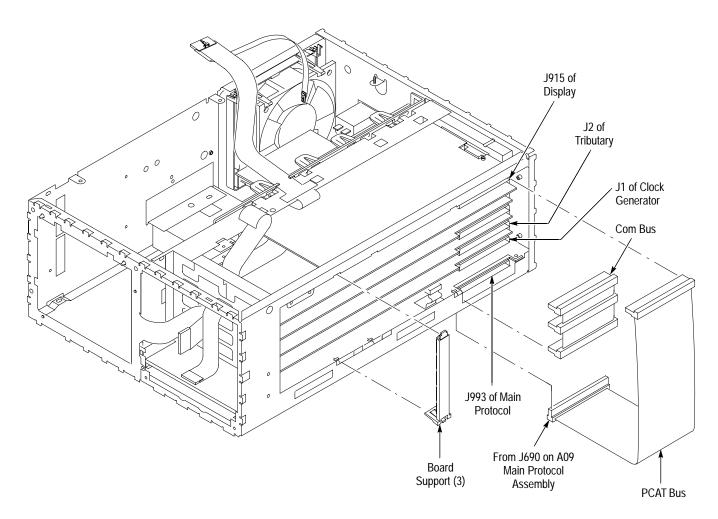

| Figure 6–23: Com Bus, Board Supports, and PCAT Bus Removal     | 6–45 |

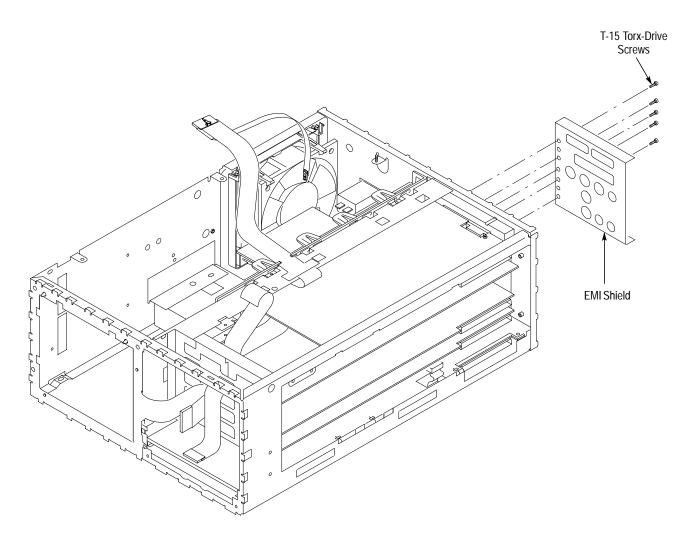

| Figure 6–24: EMI Shield Removal                                | 6–47 |

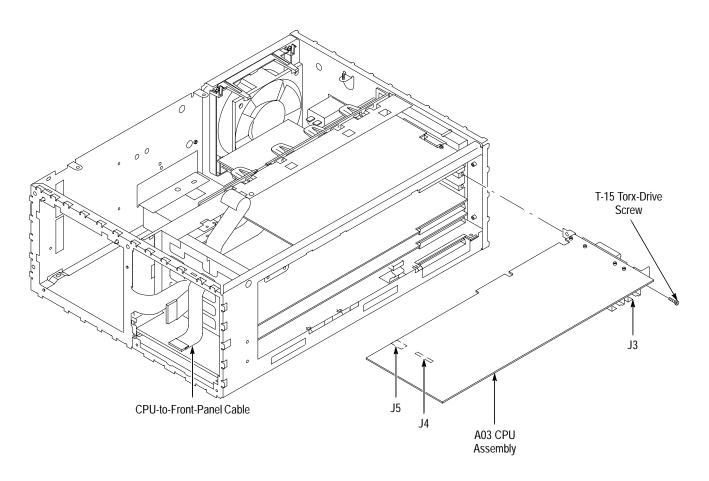

| Figure 6–25: A03 CPU Removal                                   | 6–48 |

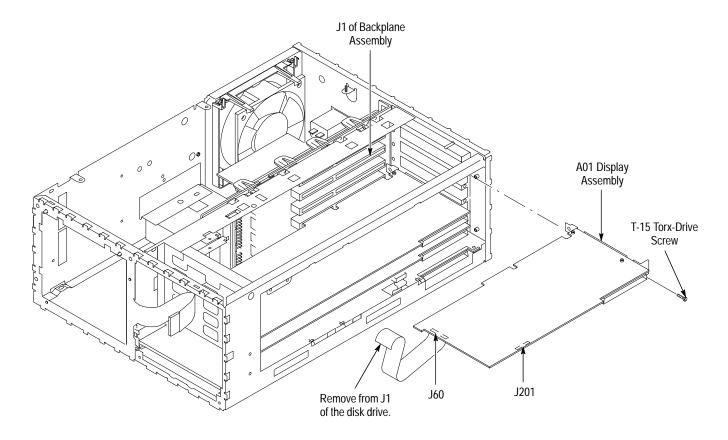

| Figure 6–26: A01 Display Assembly Removal                      | 6–50 |

| Figure 6–27: A08 Clock Generator Removal                       | 6–51 |

| Figure 6–28: Tributary Removal                                 | 6–53 |

| Figure 6–29: JAWA/JAWG Removal                                 | 6–54 |

| Figure 6–30: A02 Backplane Assembly                            | 6–56 |

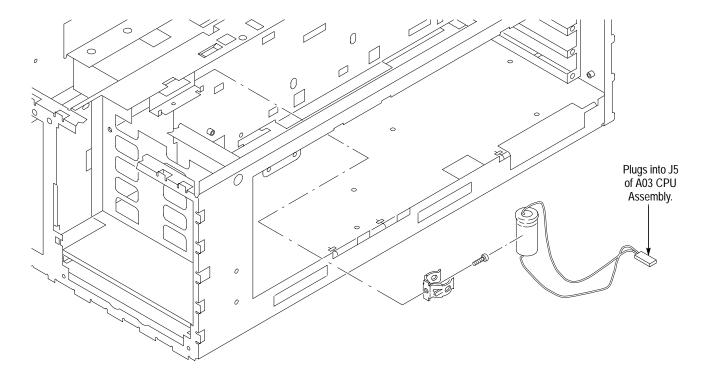

| Figure 6–31: Battery Removal                                   | 6–57 |

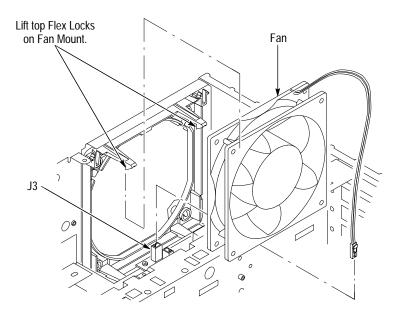

| Figure 6–32: Fan Removal                                       | 6–58 |

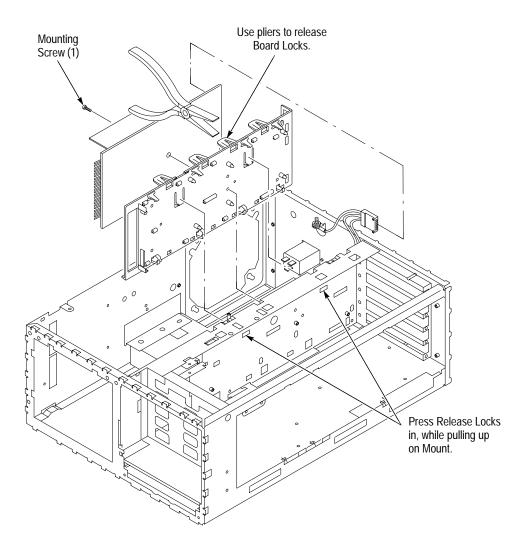

| Figure 6–33: Fan Mount Removal                                 | 6–59 |

| Figure 6–34: A25 Low Voltage Power Supply Removal              | 6-61 |

| Figure 6–35: Auxiliary Power Supply Removal                    | 6-63 |

| Figure 6–36: Line Filter Removal                               | 6-64 |

| Figure 6–37: Primary Troubleshooting Procedure                 | 6–71 |

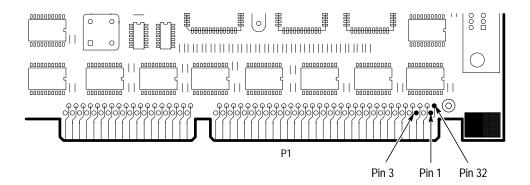

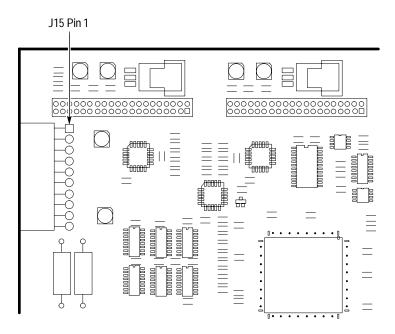

| Figure 6–38: CPU Board Connector P1                            | 6–72 |

| Figure 6–39: Backplane Troubleshooting Procedure               | 6–73 |

| Figure 6–40: Backplane Module                                  | 6–74 |

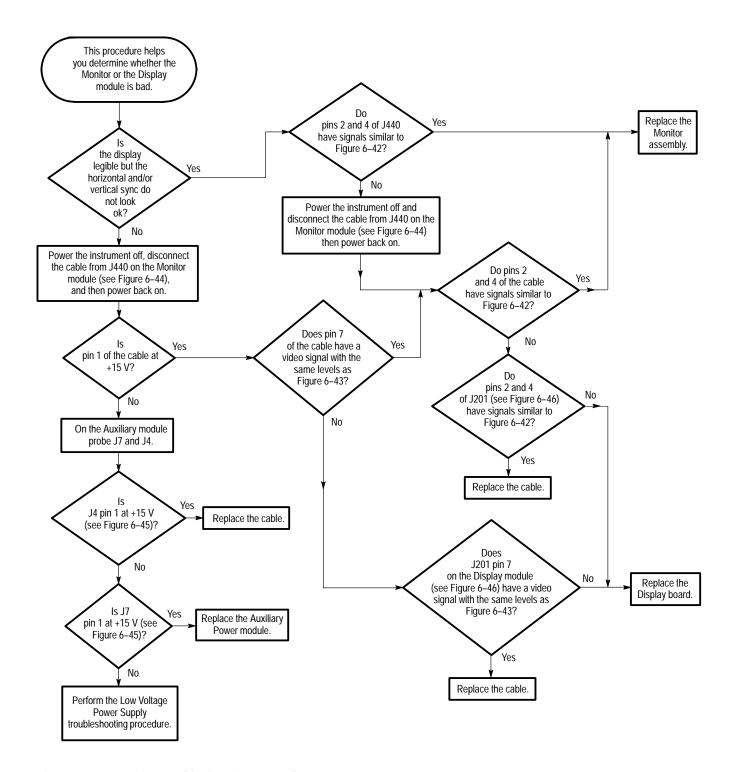

| Figure 6–41: Monitor Troubleshooting Procedure                 | 6–75 |

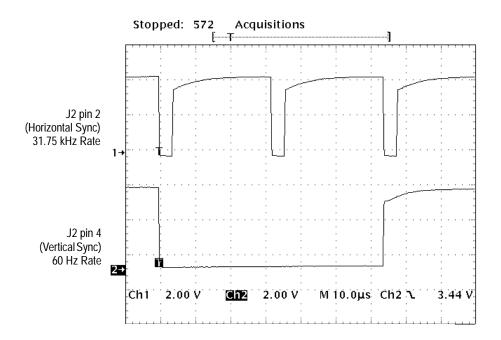

| Figure 6–42: Horizontal and Vertical Sync Signals              | 6–76 |

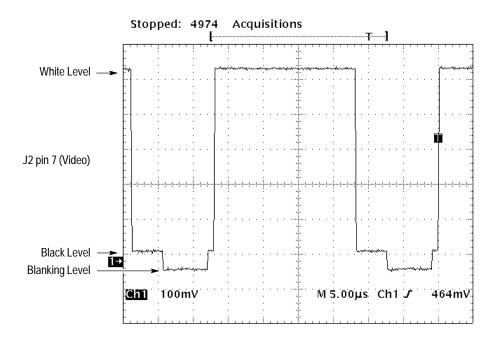

| Figure 6–43: A Video Signal with White, Black, and Blanking    | 6–76 |

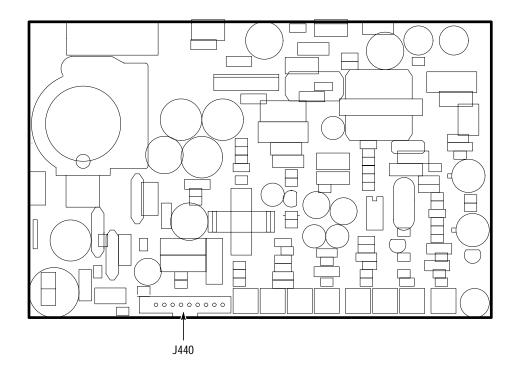

| Figure 6–44: Monitor Connector J440                            | 6–77 |

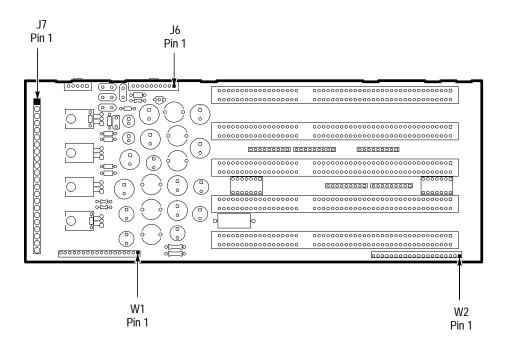

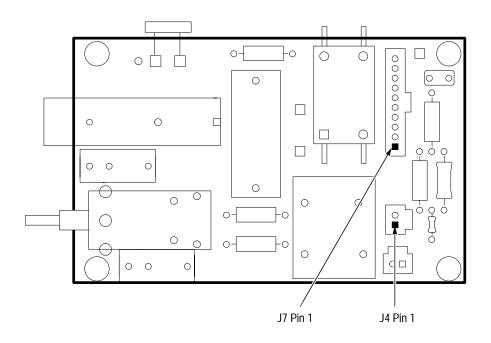

| Figure 6–45: Auxiliary Power Connectors J4 and J7              | 6–77 |

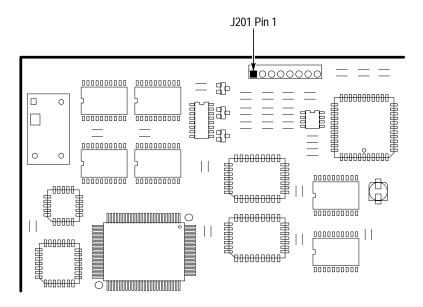

| Figure 6–46: Display Connector J201                            | 6–78 |

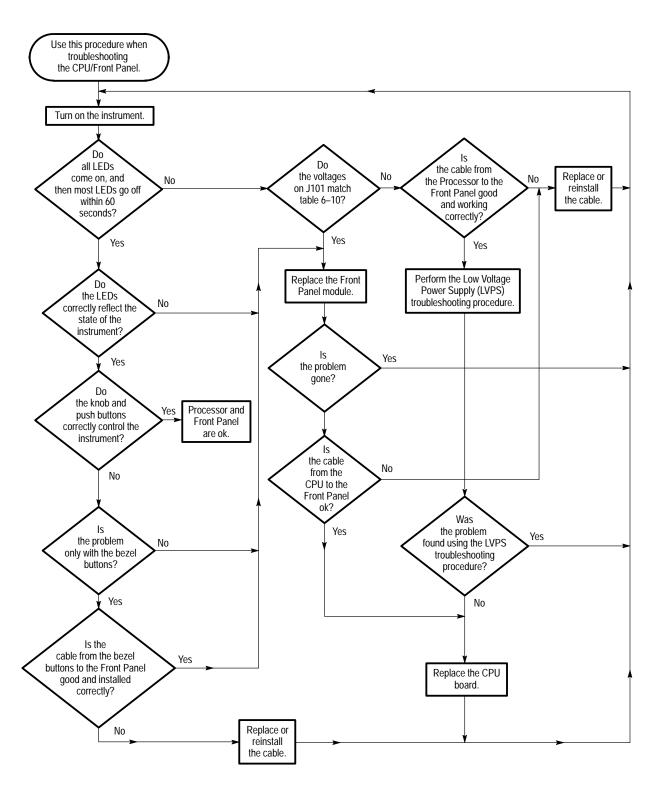

| Figure 6–47: CPU/Front Panel Troubleshooting Procedure                        | 6–79  |

|-------------------------------------------------------------------------------|-------|

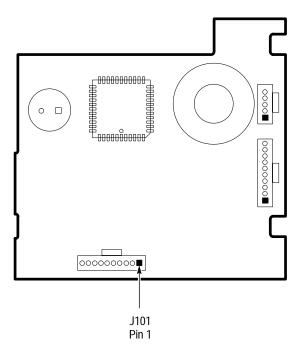

| Figure 6–48: Front Panel Board Power Connector J101                           | 6-80  |

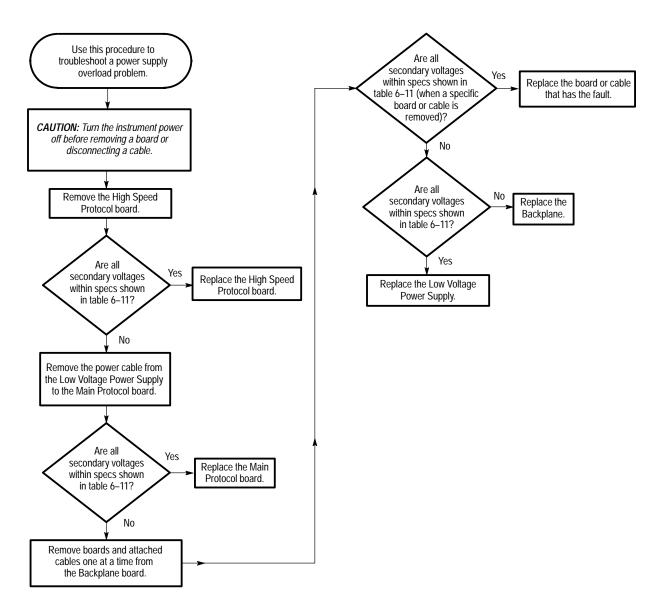

| Figure 6–49: Low Voltage Power Supply Overload Troubleshooting Procedure      | 6–81  |

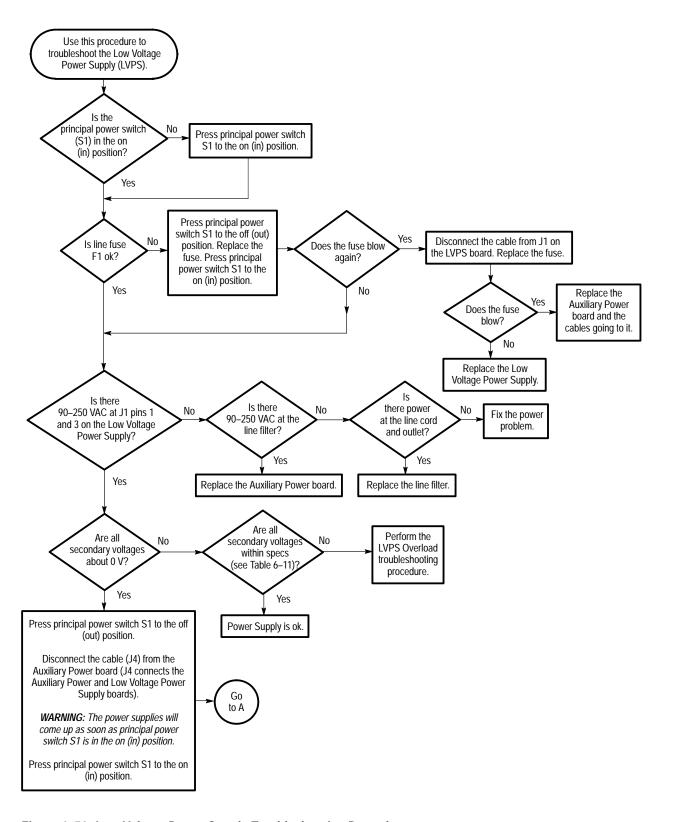

| Figure 6–50: Low Voltage Power Supply Troubleshooting Procedure               | 6–82  |

| Figure 6–51: Main Protocol Board                                              | 6-84  |

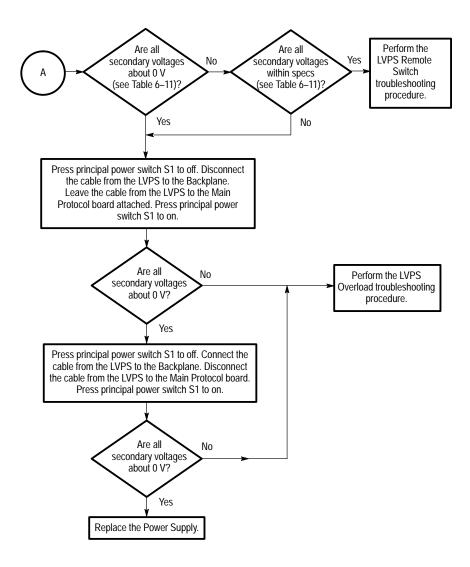

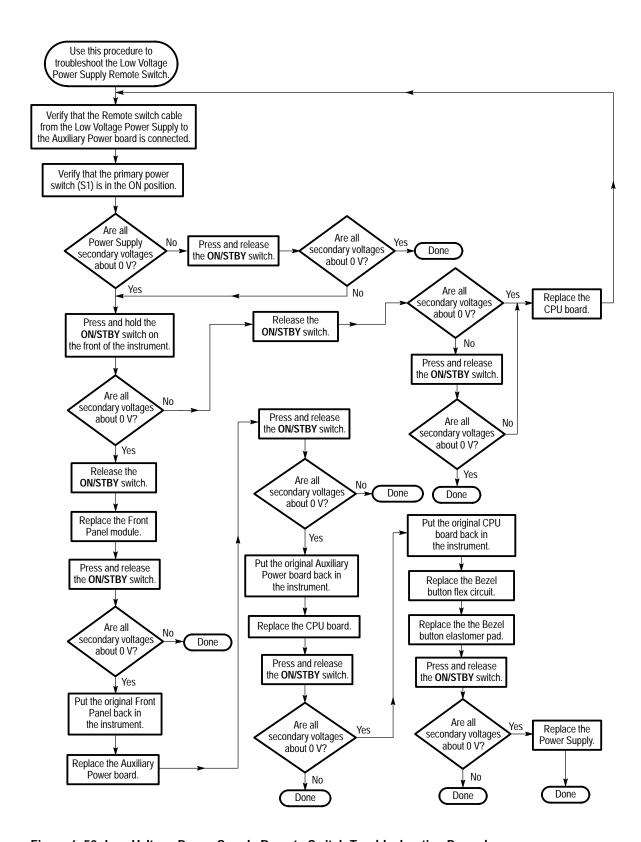

| Figure 6–52: Low Voltage Power Supply Remote Switch Troubleshooting Procedure | 6–85  |

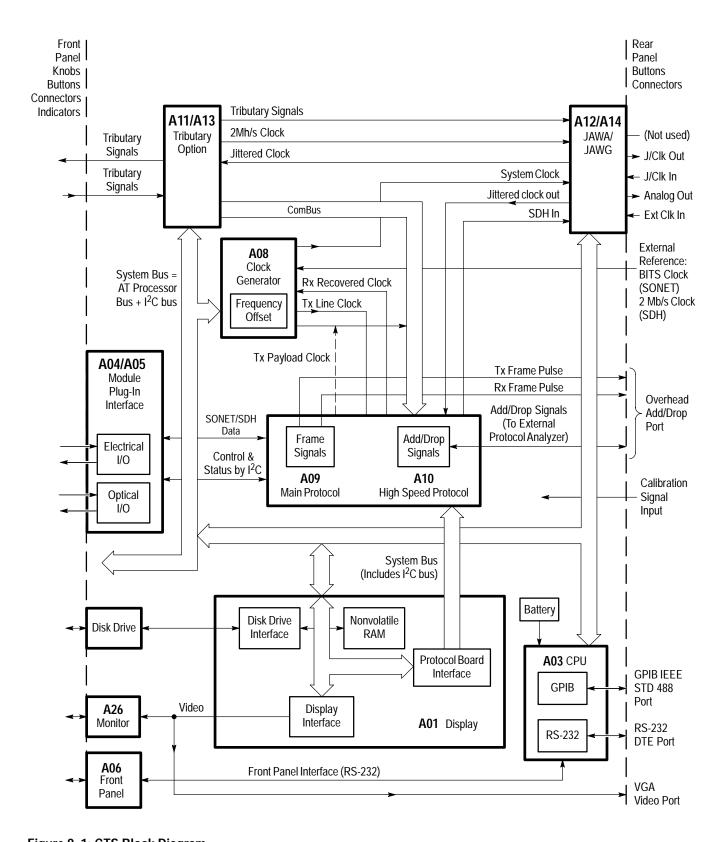

| Figure 9–1: CTS Block Diagram                                                 | 9–2   |

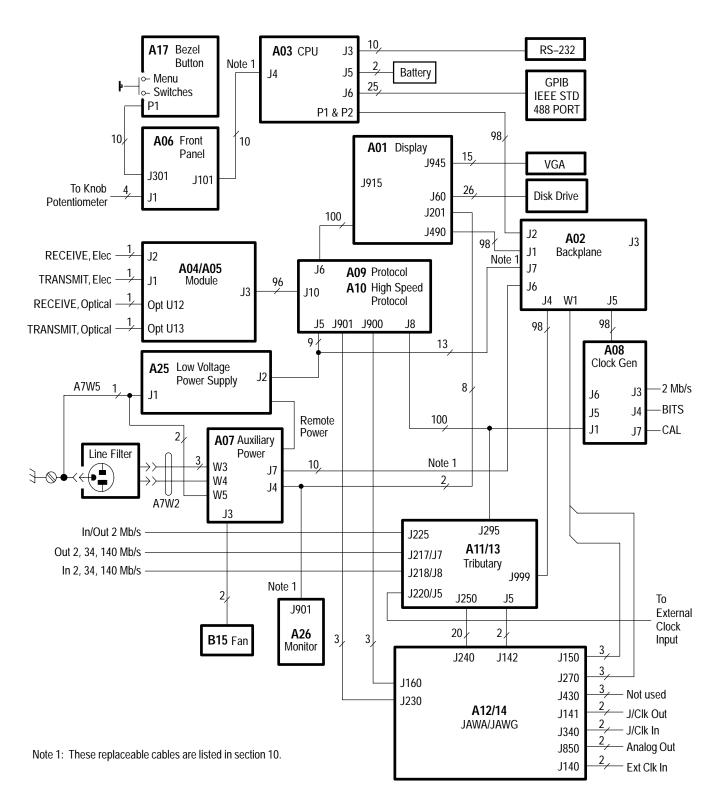

| Figure 9–2: CTS Interconnect Diagram                                          | 9–3   |

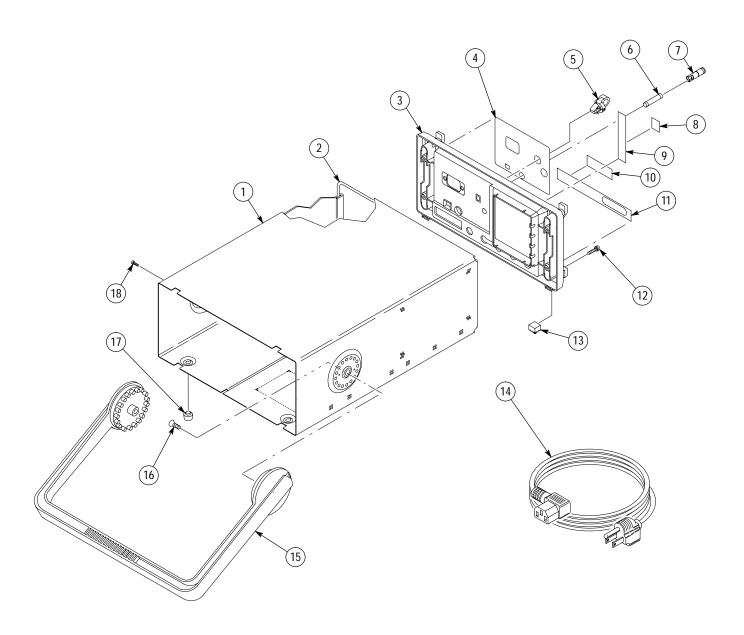

| Figure 10–1: Cabinet and Rear Panel                                           | 10-6  |

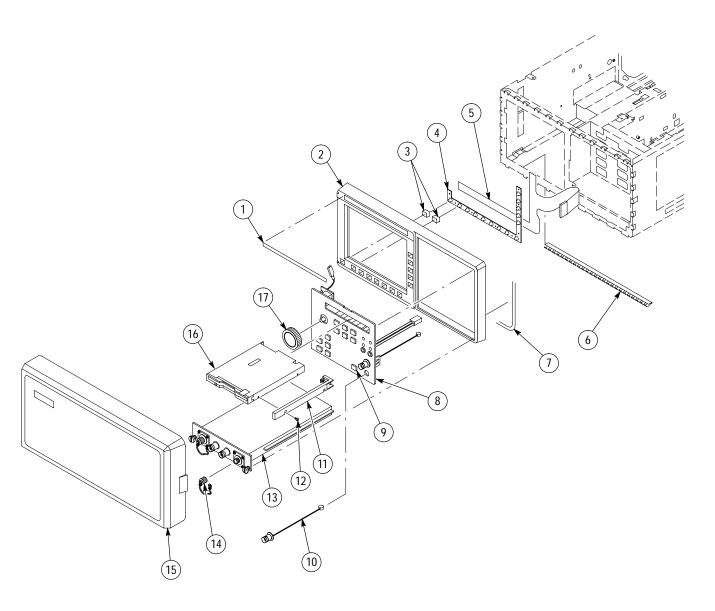

| Figure 10–2: Front Panel                                                      | 10-8  |

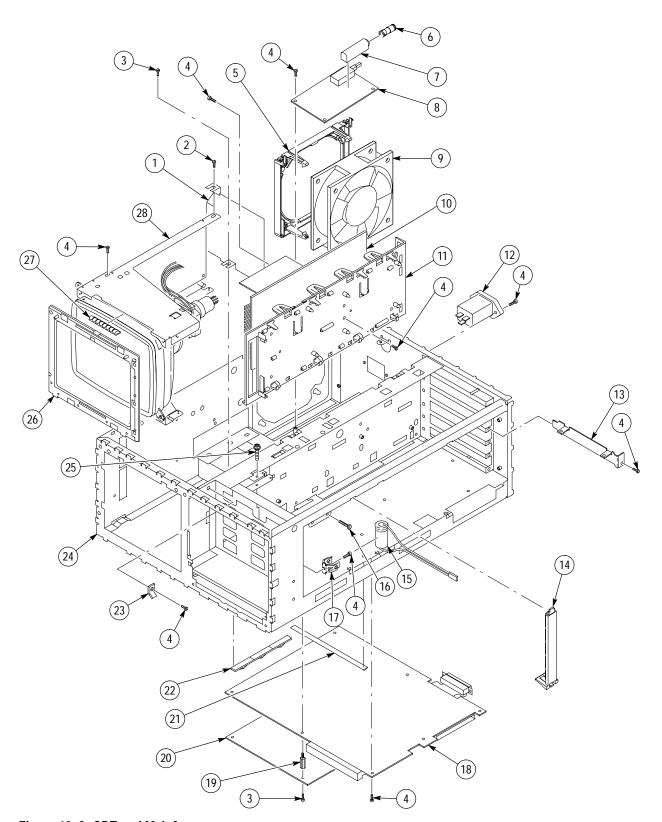

| Figure 10–3: CRT and Mainframe                                                | 10–11 |

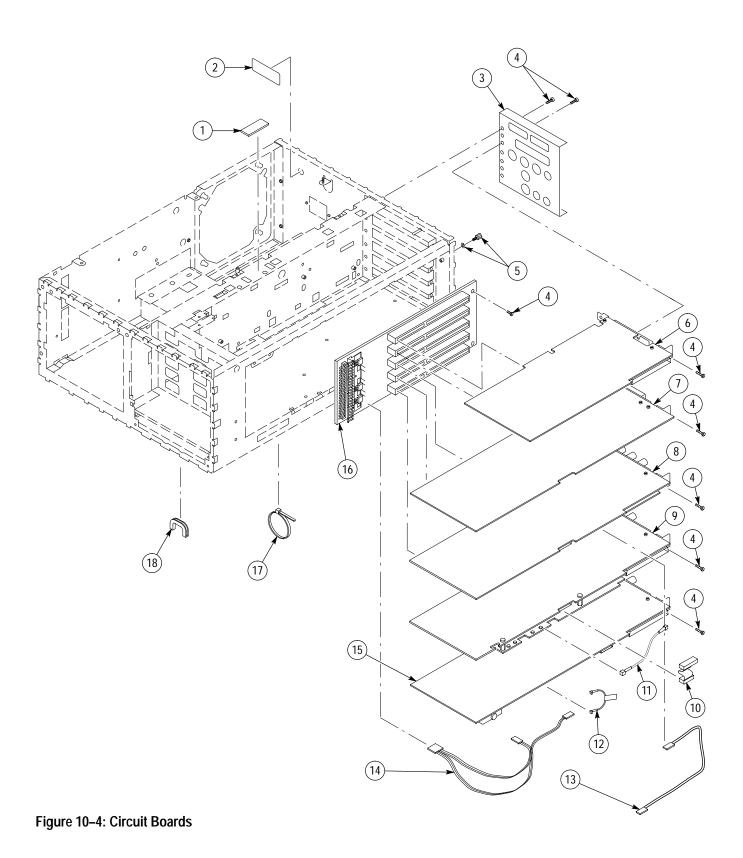

| Figure 10–4: Circuit Boards                                                   | 10-13 |

| Figure 10–5: CTS 710 Cables                                                   | 10–15 |

| Figure 10–6: CTS 750 Cables                                                   | 10–16 |

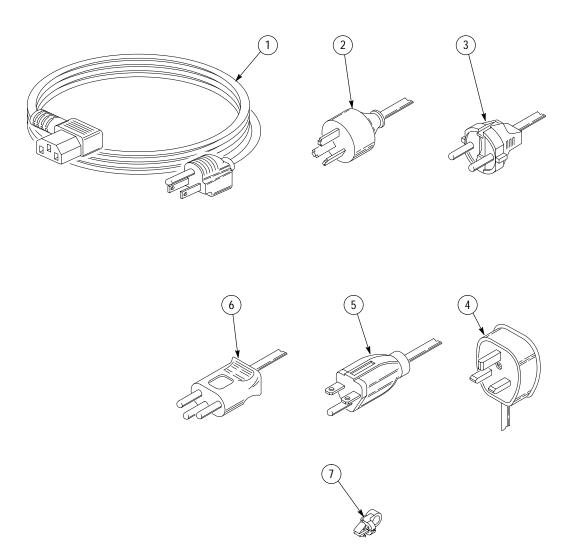

| Figure 10_7: Power Cords                                                      | 10_18 |

## **List of Tables**

| Table 1–1: Standard CTS 710 Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1–3   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Table 1–2: Option 22 DS1/DS3/VT1.5 Capabilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1–9   |

| Table 1–3: Environmental Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1–14  |

| Table 1–4: Physical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1–15  |

| Table 1–5: Certifications and compliances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1–15  |

| Table 1–6: Standard CTS 750 Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1–17  |

| Table 1–7: Option 36 2 Mb/s, 34 Mb/s, 140 Mb/s, TU12, TU3 Capabilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1–28  |

| Table 1–8: Environmental Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-25  |

| Table 1–9: Physical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-35  |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-36  |

| Table 1–10: Certifications and compliances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-30  |

| Table 2–1: Power Cord Conductor Identification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2–2   |

| Table 2–2: Power Cord Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2–2   |

| THE ALL AND MALES AND A LINE AND |       |

| Table 3–1: A09 Main Protocol Board Hardware Function Assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3–8   |

| Table 3–2: A10 High Speed Protocol Board Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-0   |

| Function Assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3–8   |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

| Table 4–1: CTS Performance Verification Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4–1   |

| Table 4–2: Required Test Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4_4   |

| Table 4–3: CTS 710 (SONET) Test Record                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4–8   |

| Table 4–4: CTS 750 (SDH) Test Record                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4–10  |

| Table 4–5: Low-Frequency Jitter Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4–113 |

| Table 4–6: Spectrum Analyzer Setups                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4–116 |

| Table 4–7: CTS Generation Setups                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4–119 |

| Table 4–8: CTS Measurement Setups                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4–121 |

| Table 4–9: Spectrum Analyzer Setups                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4–124 |